56 Rabbit 2000/3000 Microprocessor

Description

• JP (HL): The data in HL is loaded into PC. Thus the address of the next instruction fetched is

thedatainHL.

• JP (IX): The data in IX is loaded into PC. Thus the address of the next instruction fetched is

thedatainIX.

• JP (IY): The data in IY is loaded into PC. Thus the address of the next instruction fetched is

thedatainIY.

• JP mn: The 16-bit constant mn is loaded into PC. Thus the address of the next instruction

fetched is mn. This instruction recognizes labels when used in the Dynamic C assembler.

JP (HL)

JP (IX)

JP (IY)

JP mn

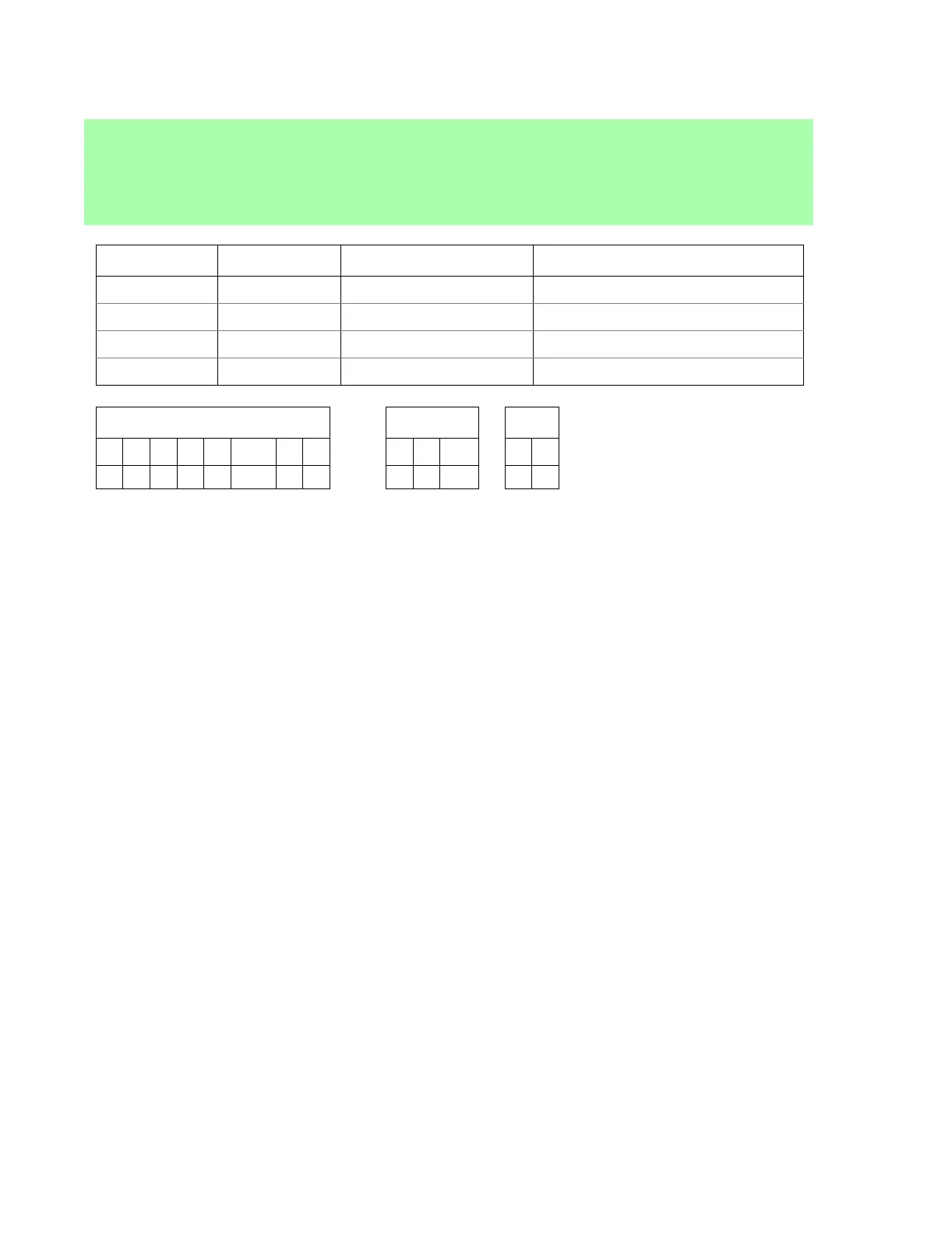

Opcode Instruction Clocks Operation

E9 JP (HL) 4 (2,2) PC = HL

DD E9 JP (IX) 6 (2,2,2) PC = IX

FD E9 JP (IY) 6 (2,2,2) PC = IY

C3 nm JP mn 7 (2,2,2,1) PC = mn

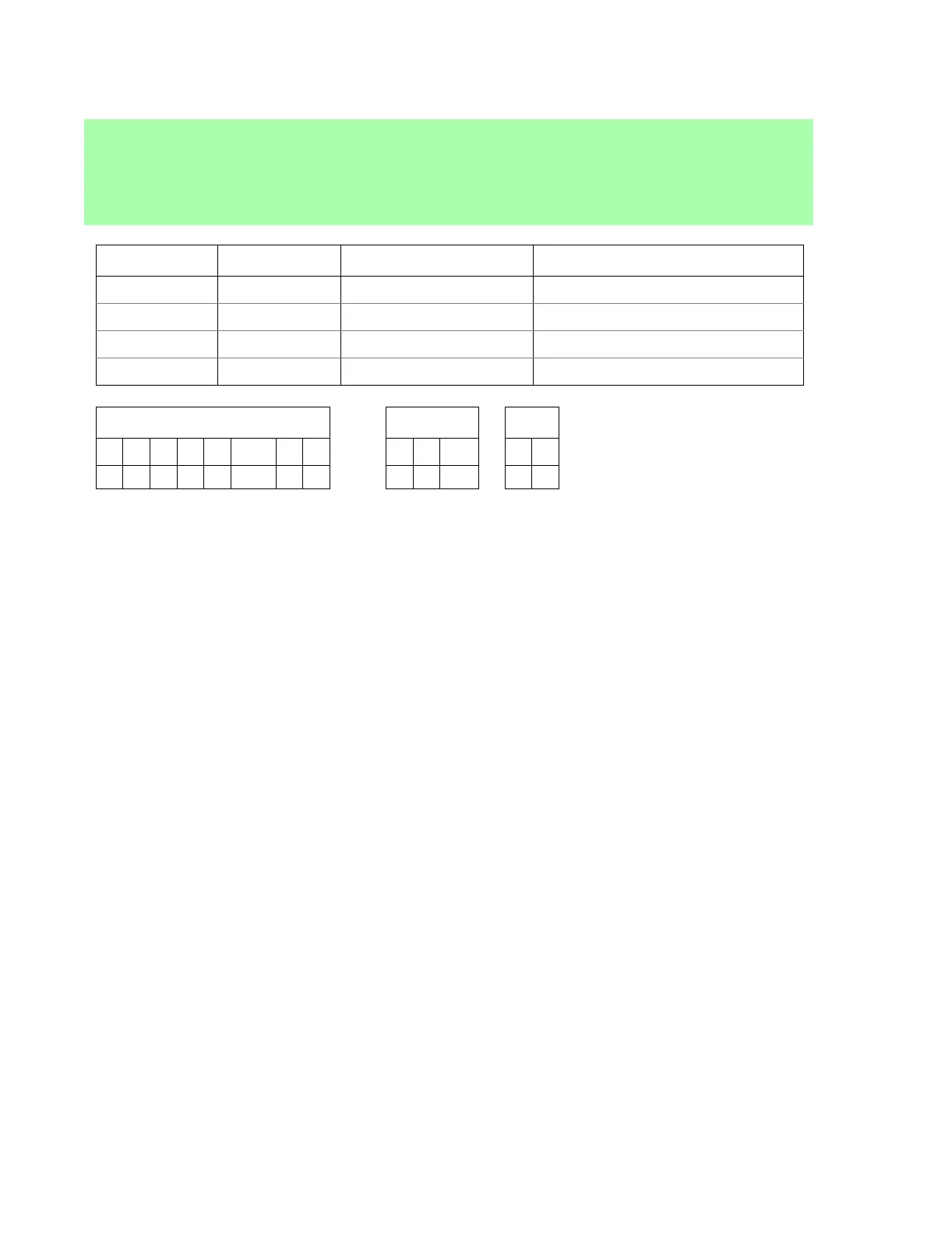

Flags ALTD I/O

S Z L/V C F R SP S D

- - - -

Loading...

Loading...