Renesas Starter Kit+ for RZ/T2M 5. User Circuitry

R20UT4939EG0100 Rev. 1.00 Page 26 of 87

Apr 20, 2022

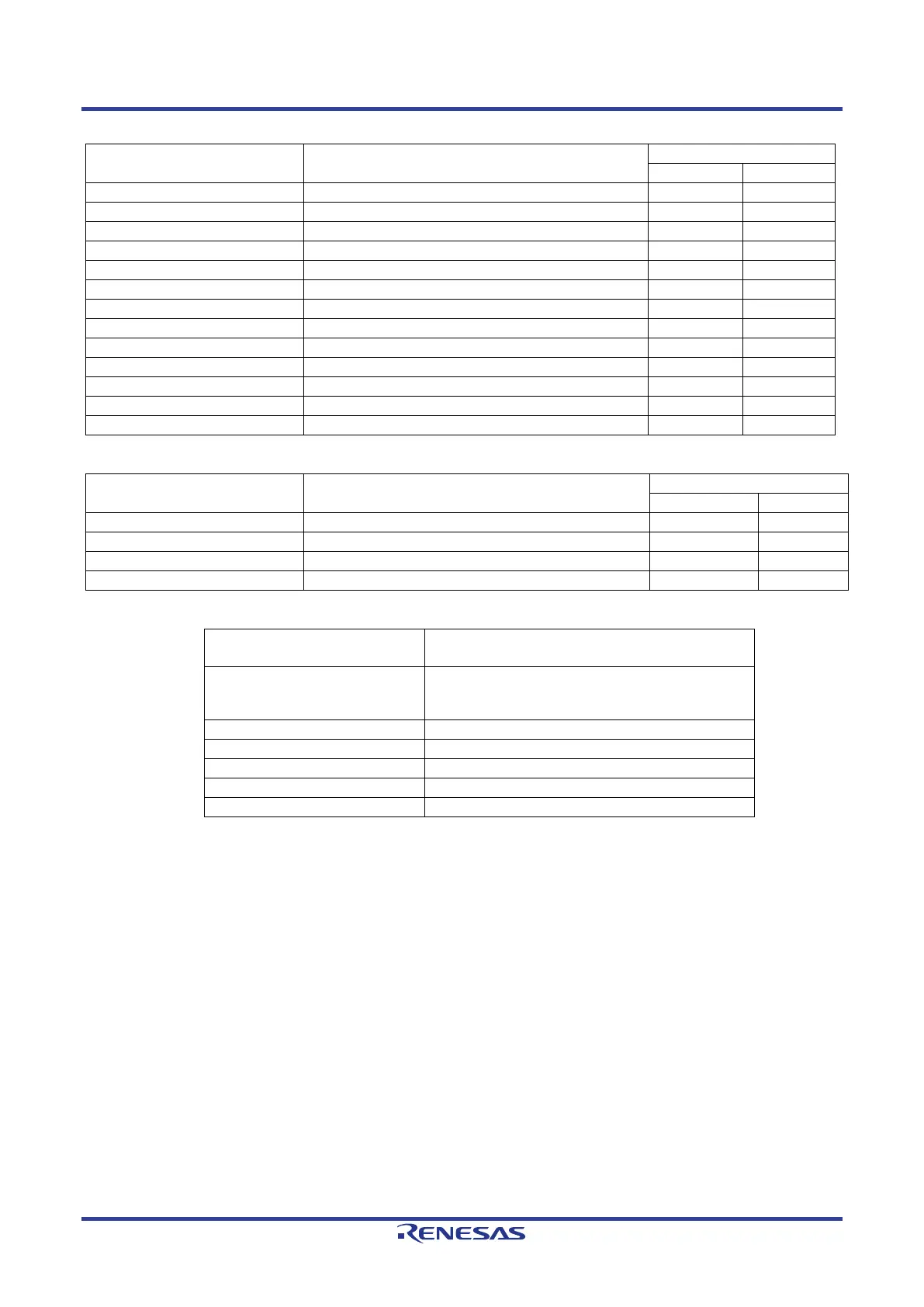

Table 5-17: Ethernet Connections (ETH2)

Ethernet signal Function

RGMII: Transmit clock output

RGMII: Transmit data enable / Transmit data error

RGMII: Receive clock input

RGMII: Receive data valid / Receive data error

Outputs 25MHz clock for EtherPHY2

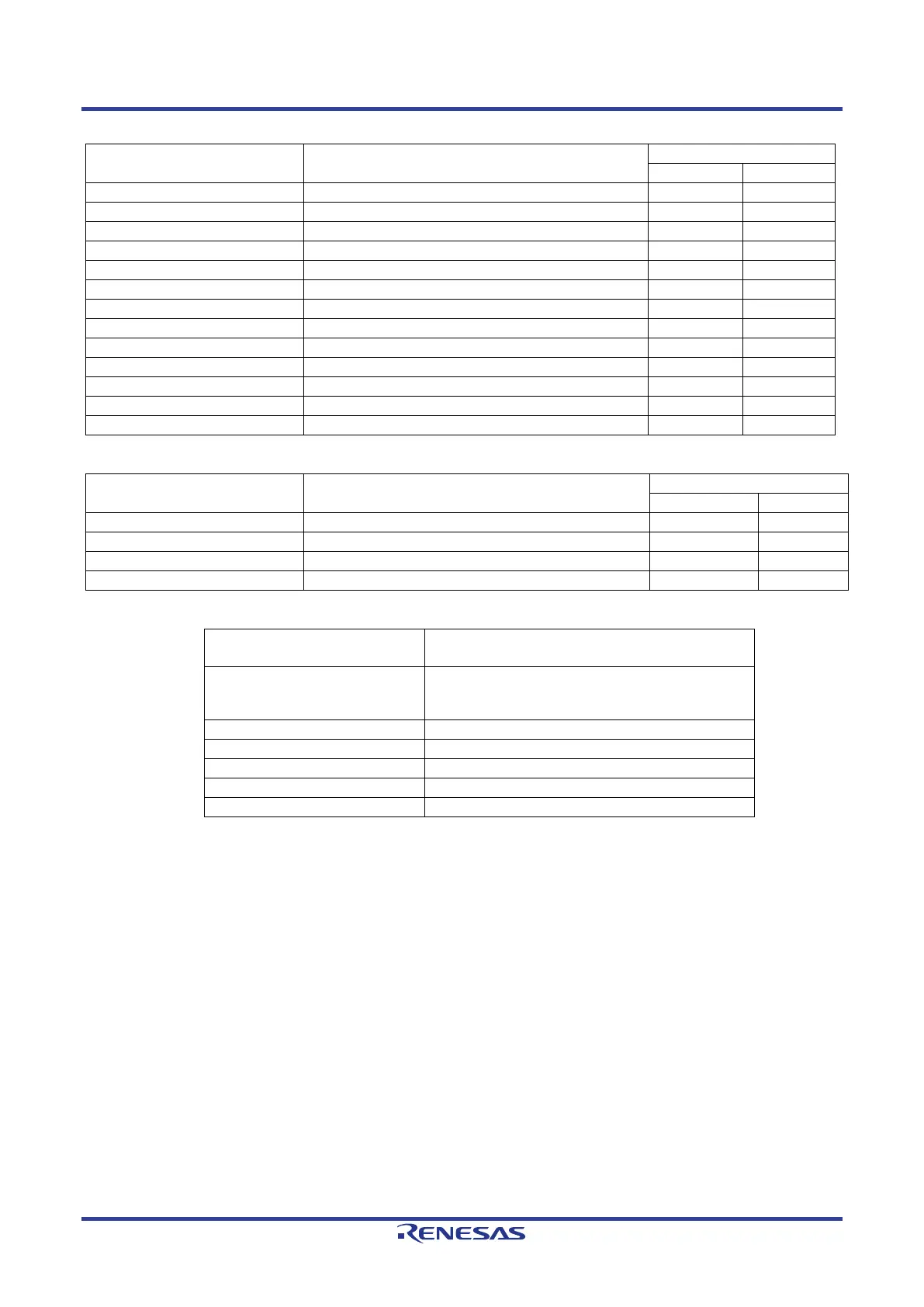

Table 5-18: Ethernet Connections (ETH0/ETH1/ETH2)

Ethernet signal Function

Table 5-19: Default PHY setting

Default PHY setting items Default PHY setting contents

PHY Address

ETH1 (IC31): = 1

Loading...

Loading...