Renesas Starter Kit+ for RZ/T2M 6. Configuration

R20UT4939EG0100 Rev. 1.00 Page 49 of 87

Apr 20, 2022

6.11 Ethernet Configuration

Table 6-31, Table 6-32, Table 6-33 below details the function of the option links associated with Ethernet

Configuration.

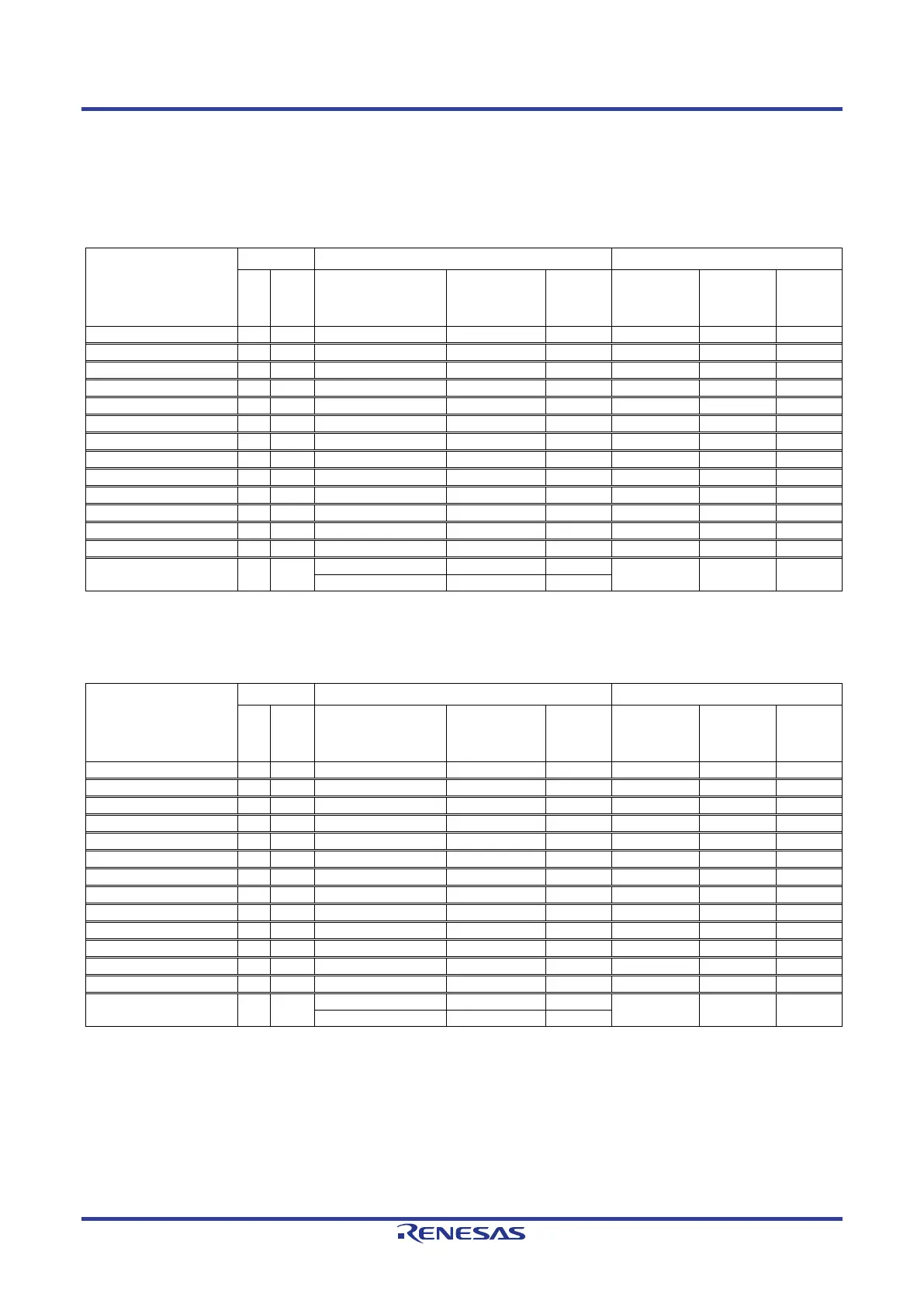

Table 6-31: Ethernet Configuration Option Links (1)

Signal name

Pin

Port

Signal Fit DNF

Interface

/Function

Fit DNF

ETH0_REFCLK_25 - -

IC35.63 R243 -

*

1

: In the default RSK+ configuration, ETH0_REFCLK_G signal is not connected to the XTAL1 pin of the

Ethernet controller IC (IC35). If you want to connect the external clock (X1) on the RSK+ to the Ethernet

controller IC, configure as shown in Table 6-31 above.

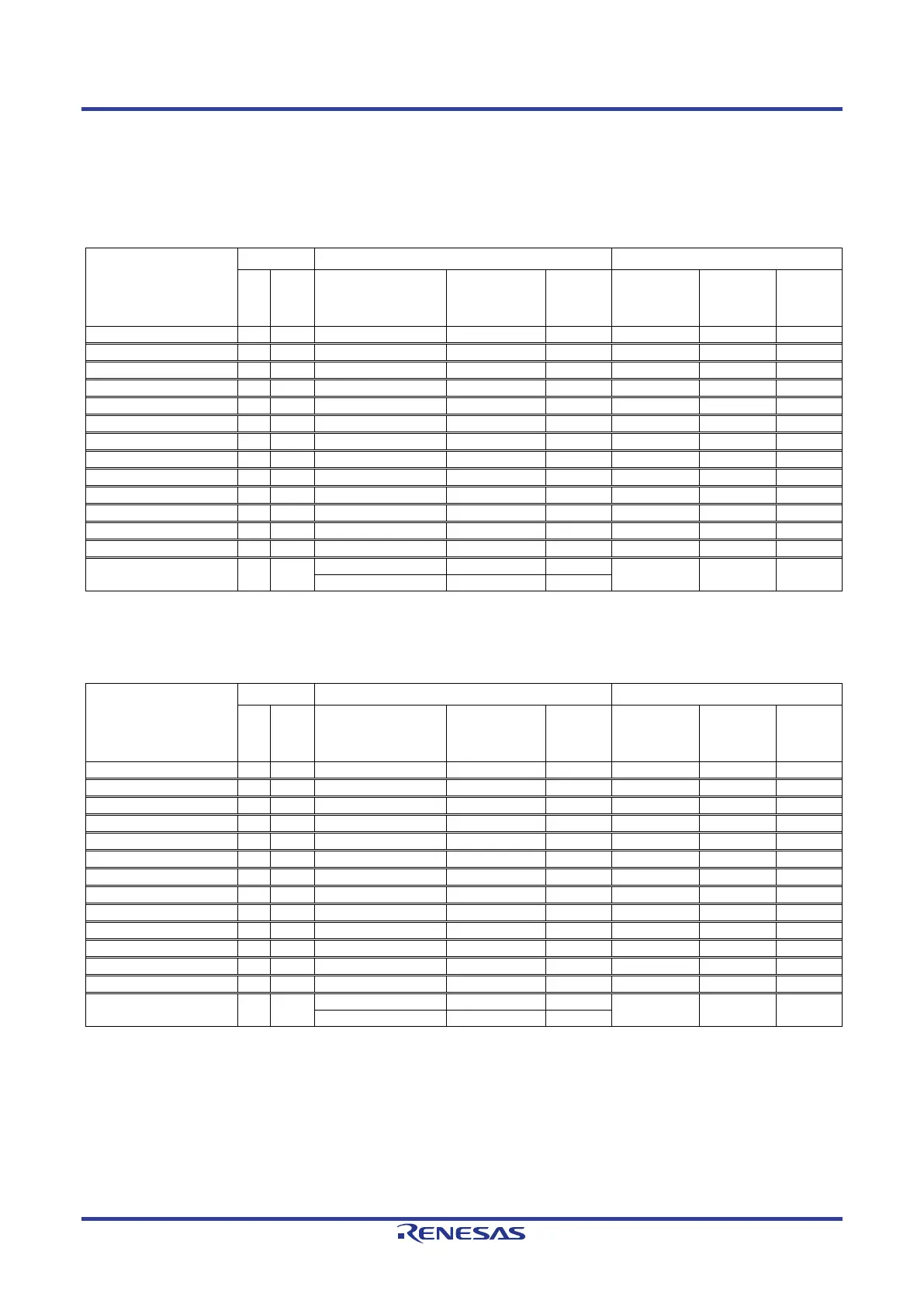

Table 6-32: Ethernet Configuration Option Links (2)

Signal name

Pin

Port

Signal Fit DNF

Interface

/Function

Fit DNF

ETH1_REFCLK_25 - -

IC31.63 R220 -

*

1

: In the default RSK+ configuration, ETH1_REFCLK_G signal is not connected to the XTAL1 pin of the

Ethernet controller IC (IC31). If you want to connect the external clock (X1) on the RSK+ to the Ethernet

controller IC, configure as shown in Table 6-32 above.

Loading...

Loading...