Renesas Starter Kit+ for RZ/T2M 5. User Circuitry

R20UT4939EG0100 Rev. 1.00 Page 25 of 87

Apr 20, 2022

5.12 Ethernet

When running any Ethernet software, a unique MAC address should be used. A unique Renesas allocated MAC

address is attached to the PCB as a sticker and should always be used with this device to ensure full compatibility

when using other Renesas hardware on a common Ethernet connection.

Three Ethernet PHY ICs are fitted to the CPU board and are connected to the MPU Ethernet peripherals. The

RZ/T2M MPU supports half and full duplex, 10Mb/s and 100Mb/s and 1000Mb/s transmission and reception.

Refer to section 5.4 Ethernet LEDs. The connections for the Ethernet controller are listed in Table 5-15, Table

5-16, Table 5-17, Table 5-18, Table 5-19 below.

Note that Ethernet port 2 cannot be used at the same time as SDRAM.

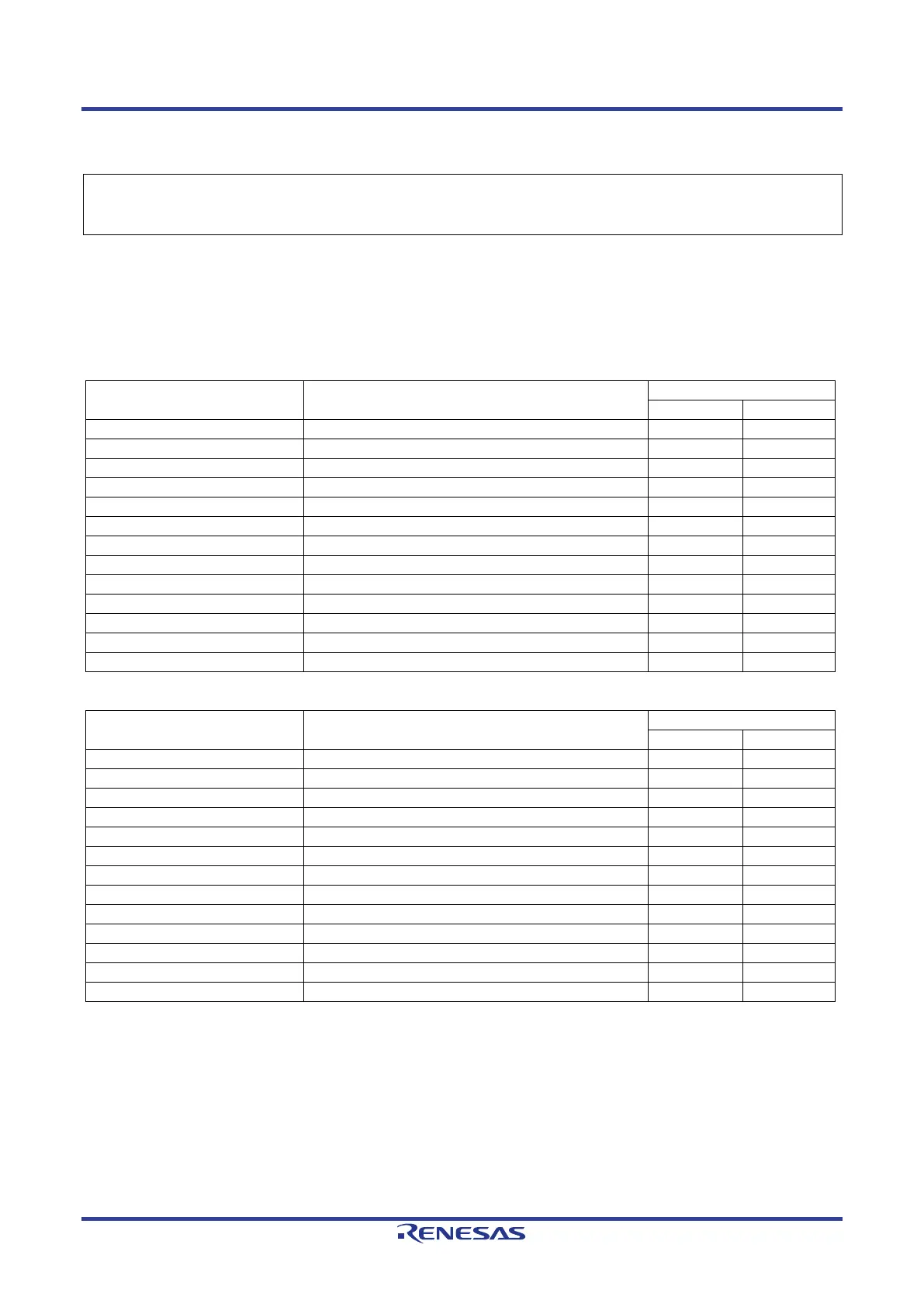

Table 5-15: Ethernet Connections (ETH0)

Ethernet signal Function

RGMII: Transmit clock output

RGMII: Transmit data enable / Transmit data error

RGMII: Receive clock input

RGMII: Receive data valid / Receive data error

Outputs 25MHz clock for EtherPHY0

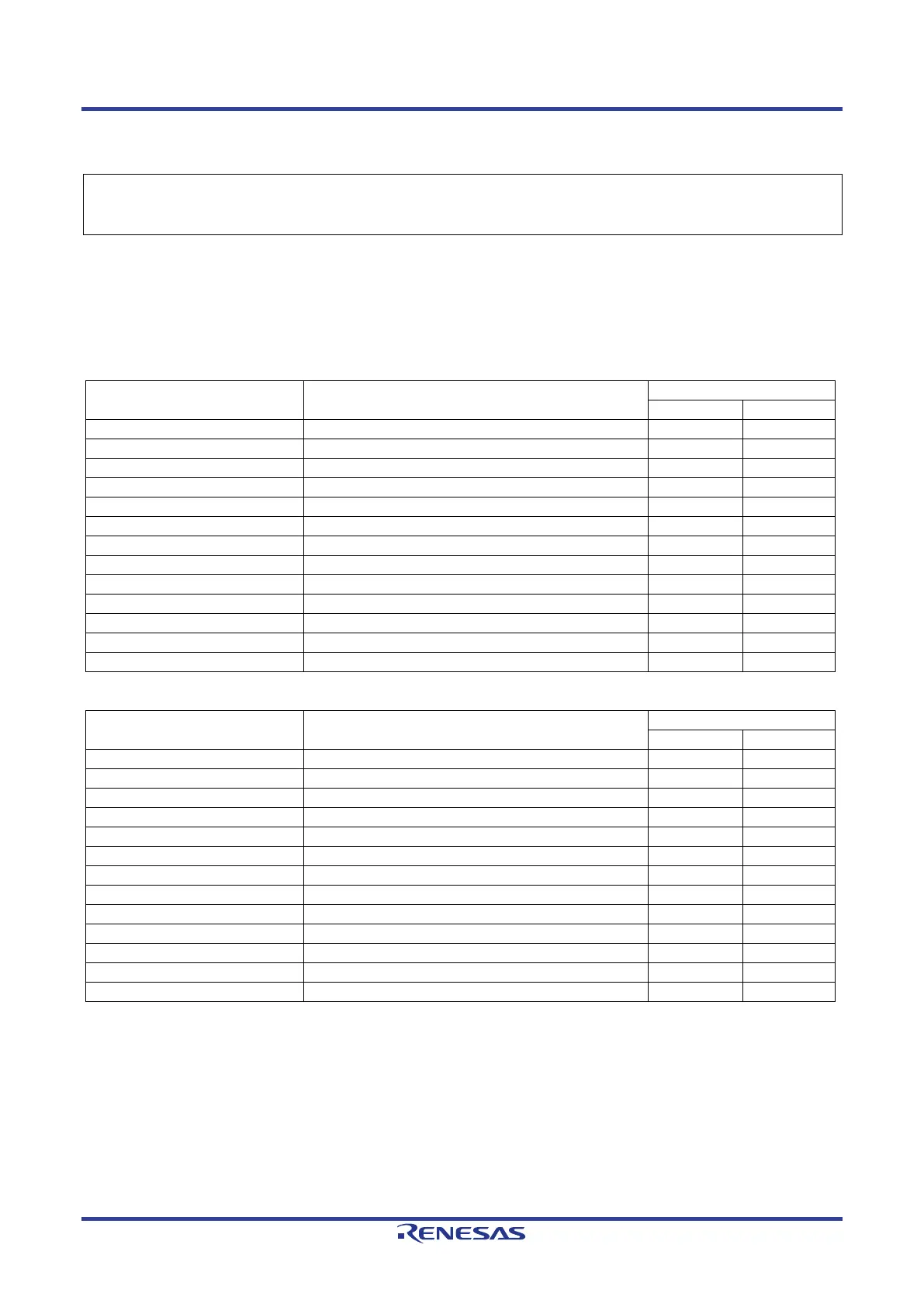

Table 5-16: Ethernet Connections (ETH1)

Ethernet signal Function

RGMII: Transmit clock output

RGMII: Transmit data enable / Transmit data error

RGMII: Receive clock input

RGMII: Receive data valid / Receive data error

Outputs 25MHz clock for EtherPHY1

Loading...

Loading...