Chapter 3 – SD Card Interface Description

Revision 2.2 SD Card Product Manual

© 2004 SanDisk Corporation 3-9 12/08/04

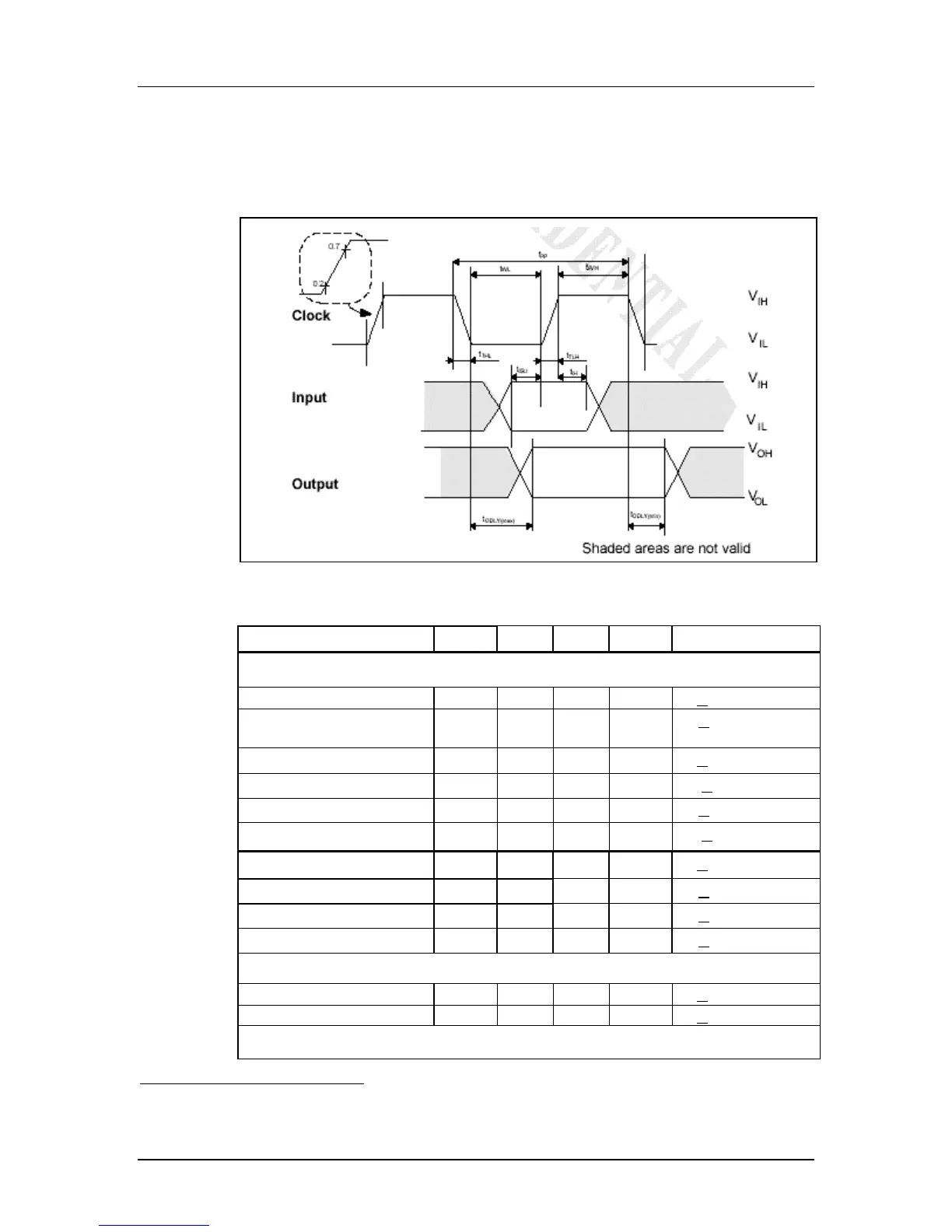

3.4.6 Bus Timing (default)

Default dataIn/dataOut timing is illustrated in Figure 3-7; bus timing parameter values are

shown in Table 3-7.

Figure 3-7 Data In/Out Referenced to Clock Timing (default)

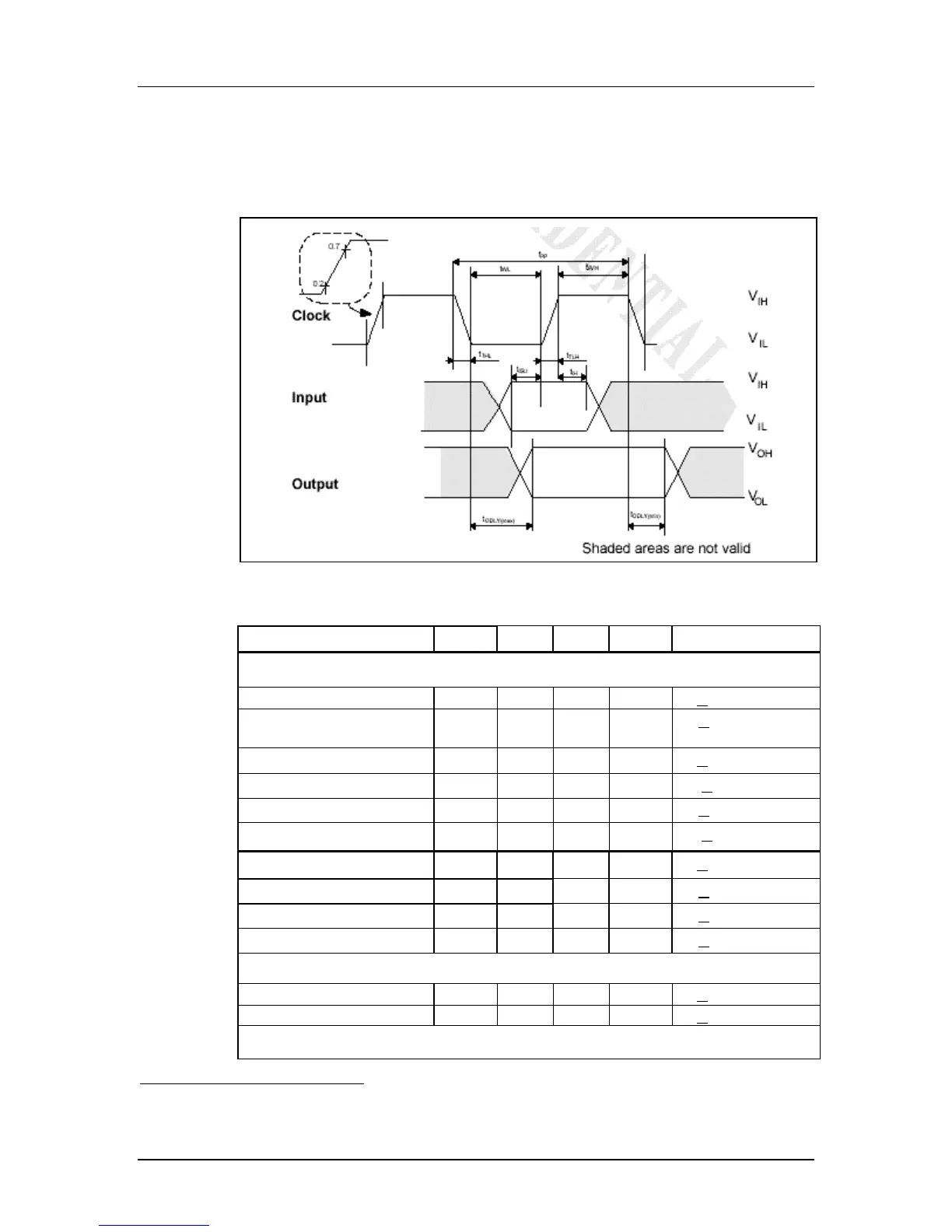

Table 3-7 Bus Timing Parameter Values (default)

Parameter Symbol Min Max Unit Remark

Clock (CLK) – all values referred to min. V

IH

and max. V

IL

Clock Freq. Data Transfer Mode f

PP

0 25 MHz C

L

< 100 pF (7 cards)

Clock Freq. Identification Mode

9

f

OD

0

10

/10

0

400 kHz C

L

< 250 pF (21 cards)

Clock Low Time t

WL

10 --- ns C

L

< 100 pF (7 cards)

Clock High Time t

WH

10 --- ns C

L

< 100 pF (7 cards)

Clock Rise Time t

TLH

--- 10 ns C

L

< 100 pF (10 cards)

Clock Fall Time t

THL

--- 10 ns C

L

< 100 pF (7 cards)

Clock Low Time t

WL

50 --- ns C

L

< 250 pF (21 cards)

Clock High Time t

WH

50 --- ns C

L

< 250 pF (21 cards)

Clock Rise Time t

TLH

--- 50 ns C

L

< 250 pF (21 cards)

Clock Fall Time t

THL

--- 50 ns C

L

< 250 pF (21 cards)

Inputs CMD, DAT – referenced to CLK

Input setup time t

ISU

5 --- ns C

L

< 25 pF (1 card)

Input hold time t

IH

5 --- ns C

L

< 25 pF (1 card)

Outputs CMD, DAT – referenced to CLK

9

Low frequency required for MMC compatibility.

10

0 Hz stops clock—given min. freq. range is for cases in which a continuous clock is required.

Loading...

Loading...