See 5.2 Performance Guidelines for Outputs.

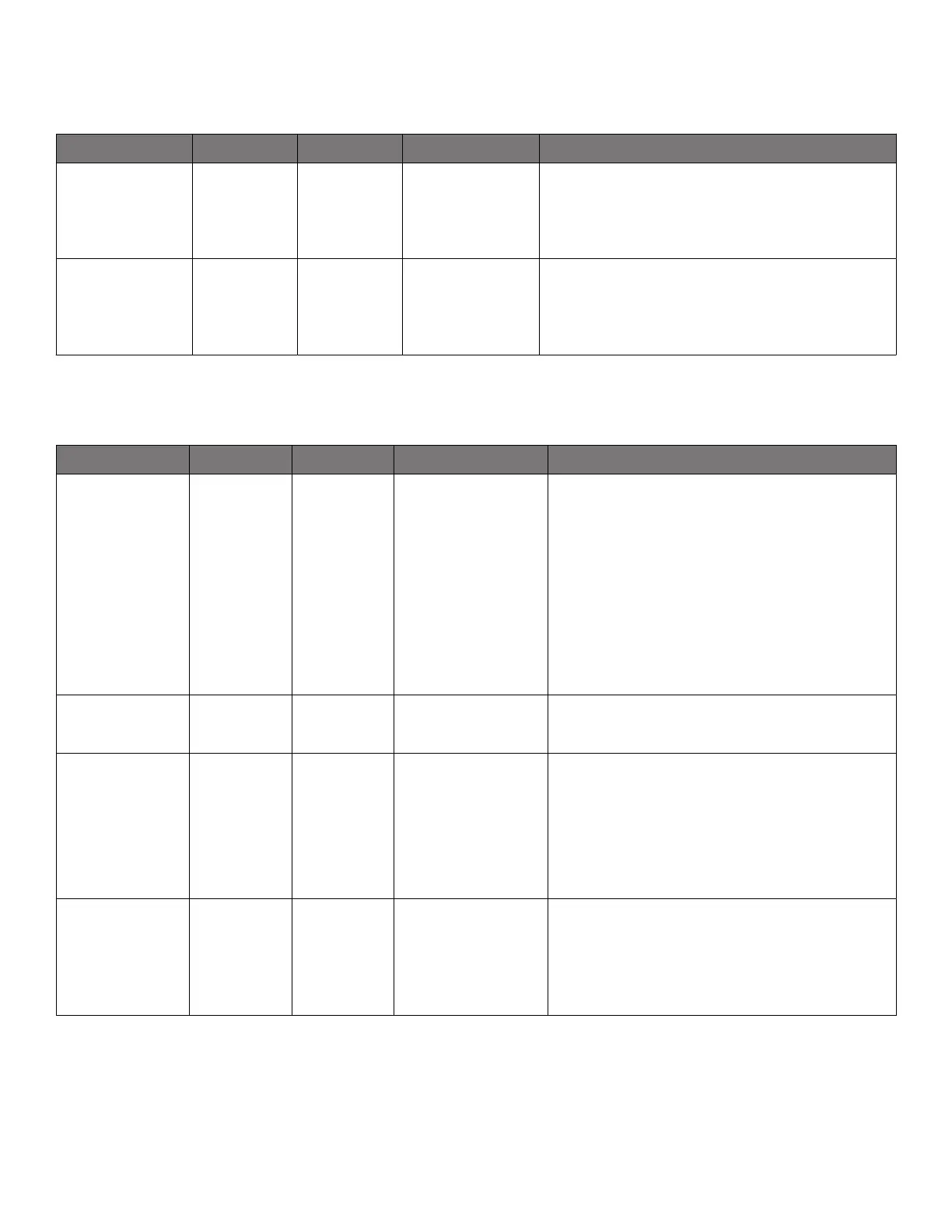

Table 14.43. 0x010A Clock Output 0 Amplitude and Common Mode Voltage

Reg Address Bit Field Type Setting Name Description

0x010A 3:0 R/W OUT0_CM This field only applies when OUT0_FORMAT=1 or 2.

See Table 5.4 Settings for LVDS, LVPECL, and HCSL

on page 25 and 15. Appendix—Setting the Differential

Output Driver to Non-Standard Amplitudes for details of

the settings.

0x010A 6:4 R/W OUT0_AMPL This field only applies when OUT0_FORMAT=1, 2, or 3.

See Table 5.4 Settings for LVDS, LVPECL, and HCSL

on page 25 and 15. Appendix—Setting the Differential

Output Driver to Non-Standard Amplitudes for details of

the settings.

ClockBuilder Pro sets the correct common mode voltage and amplitude for LVDS, LVPECL, and HCSL outputs.

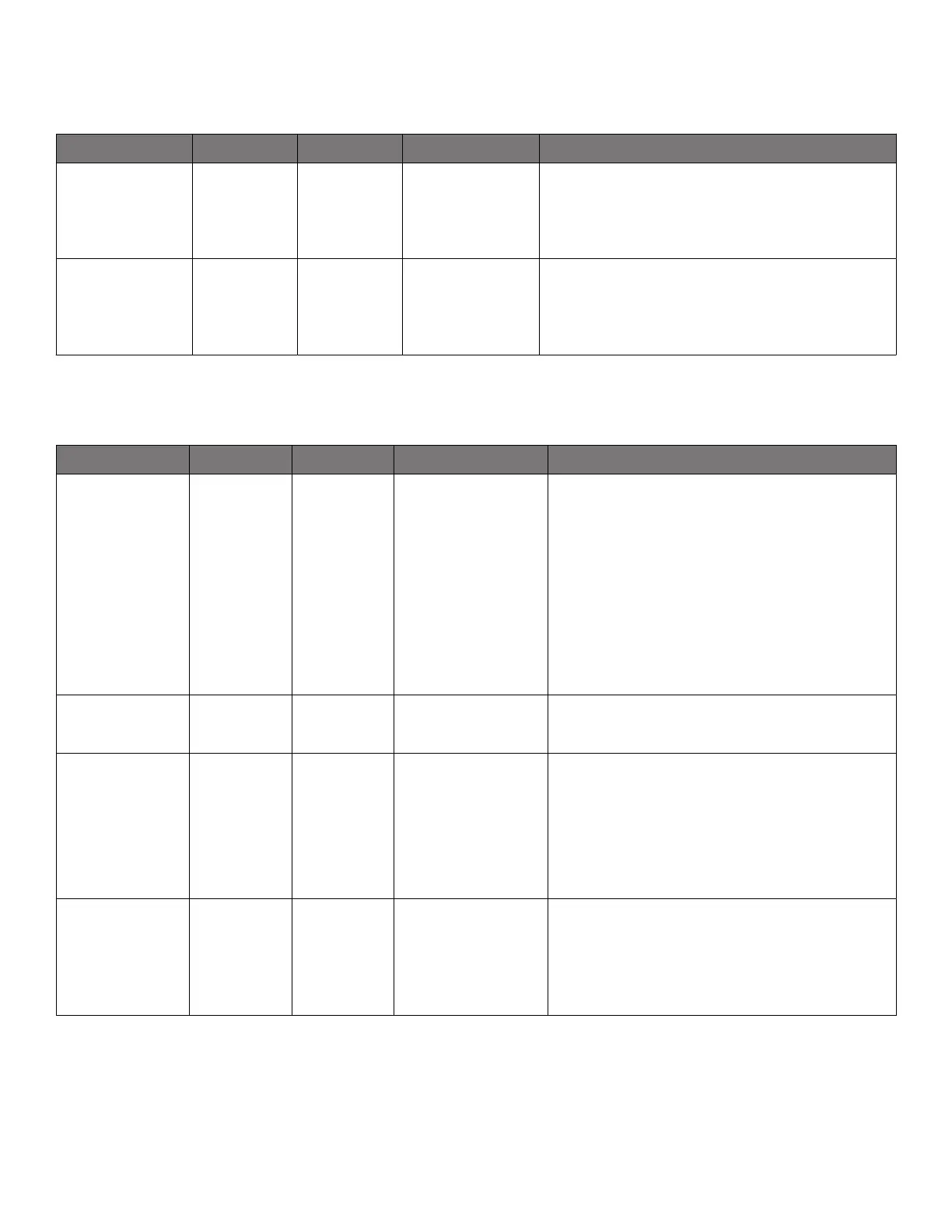

Table 14.44. 0x010B Clock Output 0 Mux and Inversion

Reg Address Bit Field Type Setting Name Description

0x010B 2:0 R/W OUT0_MUX_SEL

Output driver 0 input mux select.This selects the multi-

synth (N divider) that is connected to the output driver.

0: N0

1: N1

2: N2

3: N3

4: N4

5-7: Reserved

0x010B 3 R/W OUT0_VDD_SEL_EN Output Driver VDD Select Enable. Set to 1

for normal operation.

0x010B 5:4 R/W OUT0_VDD_SEL Output Driver VDD Select

0: 3.3V

1: 1.8V

2: 2.5V

3: Reserved

0x010B 7:6 R/W OUT0_INV 0: CLK and CLKb not inverted

1: CLKb inverted

2: CLK and CLKb inverted

3: CLK inverted

Each of the 10 output drivers can be connected to any of the five N dividers. More than one output driver can connect to the same N

divider.

The 10 output drivers are all identical. The single set of descriptions above for output driver 0 applies to the other nine output drivers.

Si5341, Si5340 Rev D Family Reference Manual • Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

70 Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 70

Loading...

Loading...