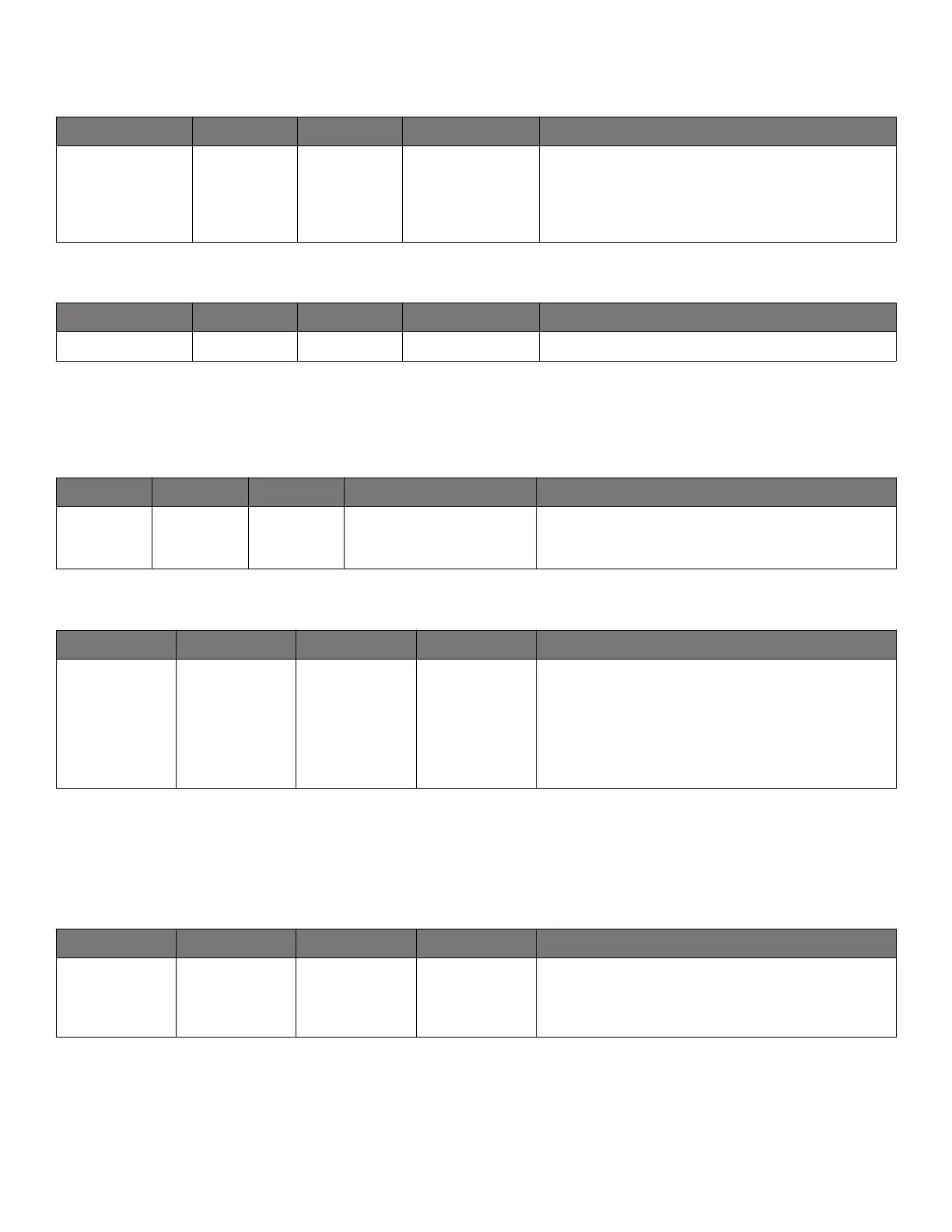

Table 14.85. 0x094A Input Clock Routing Enable

Reg Address Bit Field Type Setting Name Description

0x094A 6:4 R/W INx_TO_PFD_EN When = 1, enables the routing of the 3 input clocks

IN0,1,2 to the Phase Detector. Each bit corresponds

to the inputs as follows [6:4] = [IN2 IN1 IN0]. IN_SEL

is used to select the input clock that is applied to the

phase detector.

Table 14.86. 0x095E

Reg Address Bit Field Type Setting Name Description

0x095E 0 R/W M_INTEGER Set by CBPro

14.2.6 Page A Registers Si5341

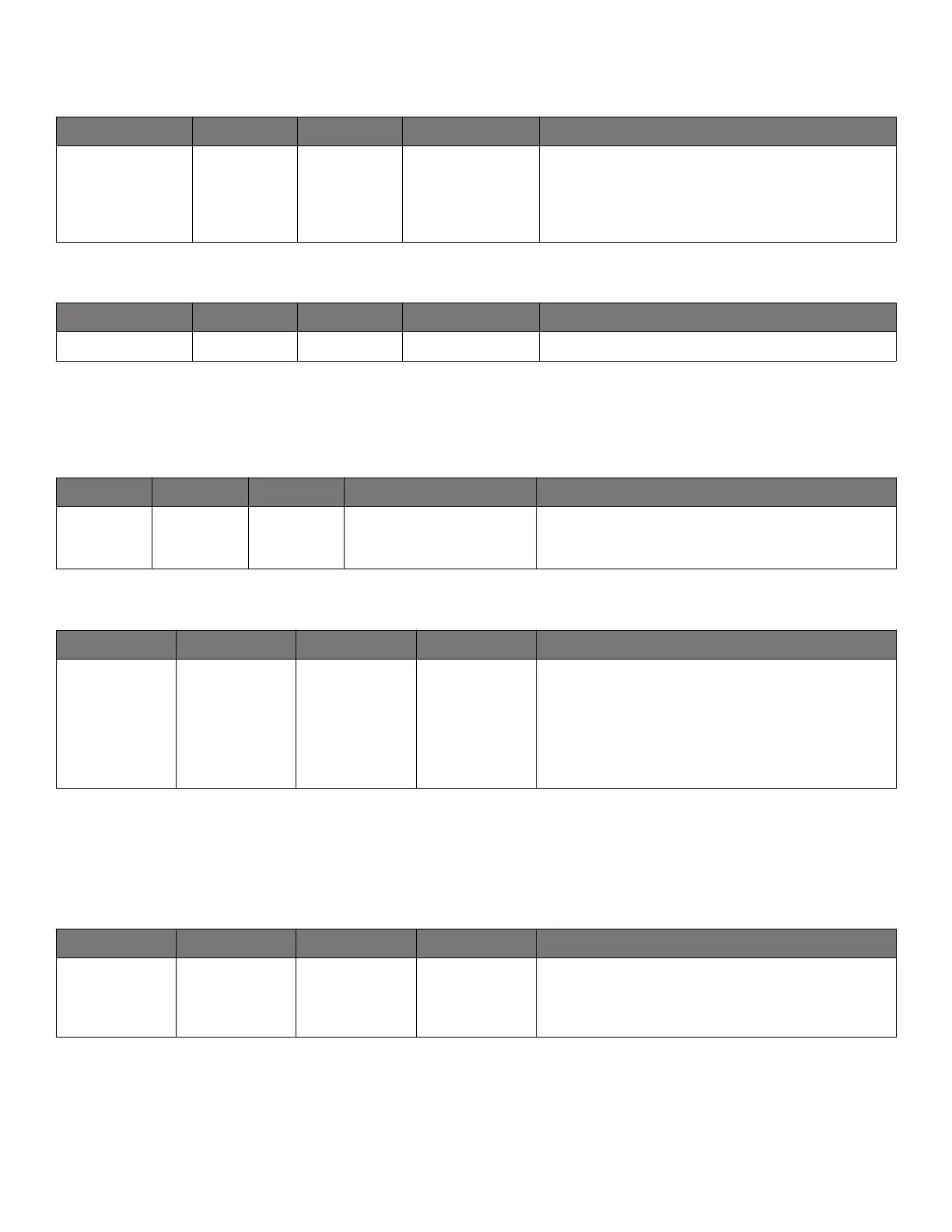

Table 14.87. 0x0A03 N Divider Clocks

Reg Address Bit Field Type Name Description

0x0A03 4:0 R/W N_CLK_TO_OUTX_EN Bits in this field correspond to the N dividers as [N4 N3

N2 N1 N0]. If an N divider is used, the corresponding bit

must be 1. See also registers 0x0A05 and 0x0B4A[4:0]

Table 14.88. 0x0A04 N Divider Phase Interpolator Bypass

Reg Address Bit Field Type Name Description

0x0A04 4:0 R/W N_PIBYP Bypasses the Phase Interpolator of the N Multisynth di-

vider. Set to a 1 when the value of N divider is integer

and will not be used as a DCO. Set to a 0 when the

value of N is fractional (used as a DCO). Slightly lower

output jitter may occur when the Phase Interpolator is

bypassed (=1). Bits in this field correspond to the N

dividers as [N4 N3 N2 N1 N0]

A soft reset reg 0x001C [0] should be asserted after changing any of these bits. If it is expected that any of the N dividers will

be changing from integer to fractional, it is recommended that the corresponding bits be initialized to 0 so that when the change

from integer to fractional occurs there will be no need for a soft reset. For this reason DCO (digitally controlled oscillator) and FOTF

(frequency on the fly) applications should have zeros for these bits. See DCO Applications with Jitter Attenuators .

Table 14.89. 0x0A05 N Divider Power Down

Reg Address Bit Field Type Name Description

0x0A05 4:0 R/W N_PDNB Powers down the N divider. If an N divider is not used,

set the respective bit to 0 to power it down. Bits in this

field correspond to the N dividers as [N4 N3 N2 N1 N0].

See also registers 0x0A03 and 0x0B4A[4;0]

Si5341, Si5340 Rev D Family Reference Manual • Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

83 Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 83

Loading...

Loading...