14.3.2 Page 1 Registers Si5340

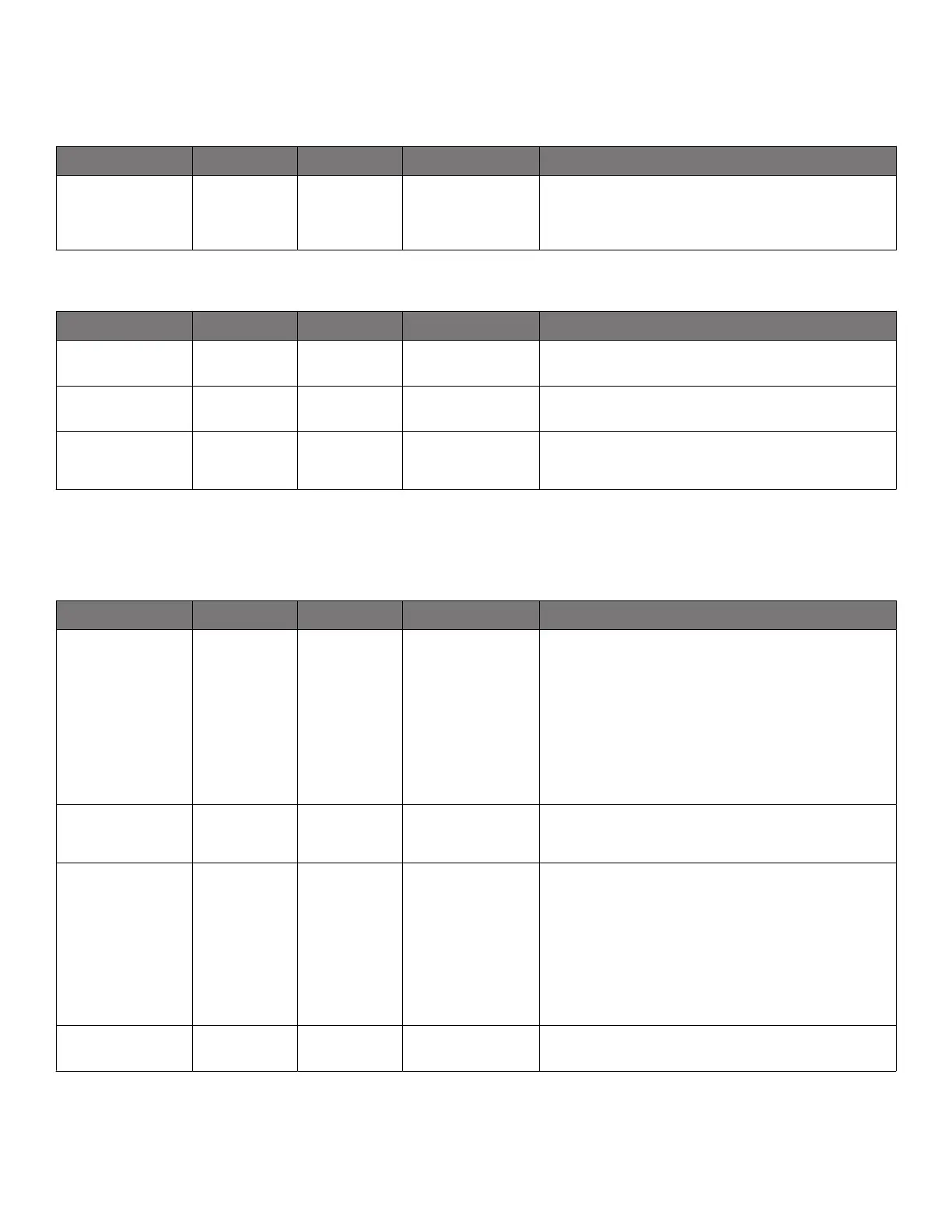

Table 14.131. 0x0102 All Output Clock Driver Disable

Reg Address Bit Field Type Setting Name Description

0x0102 0 R/W OUTALL_DISA-

BLE_LOW

0 disables all output drivers

1 no output drivers are disabled by this bit but other

signals may disable the outputs.

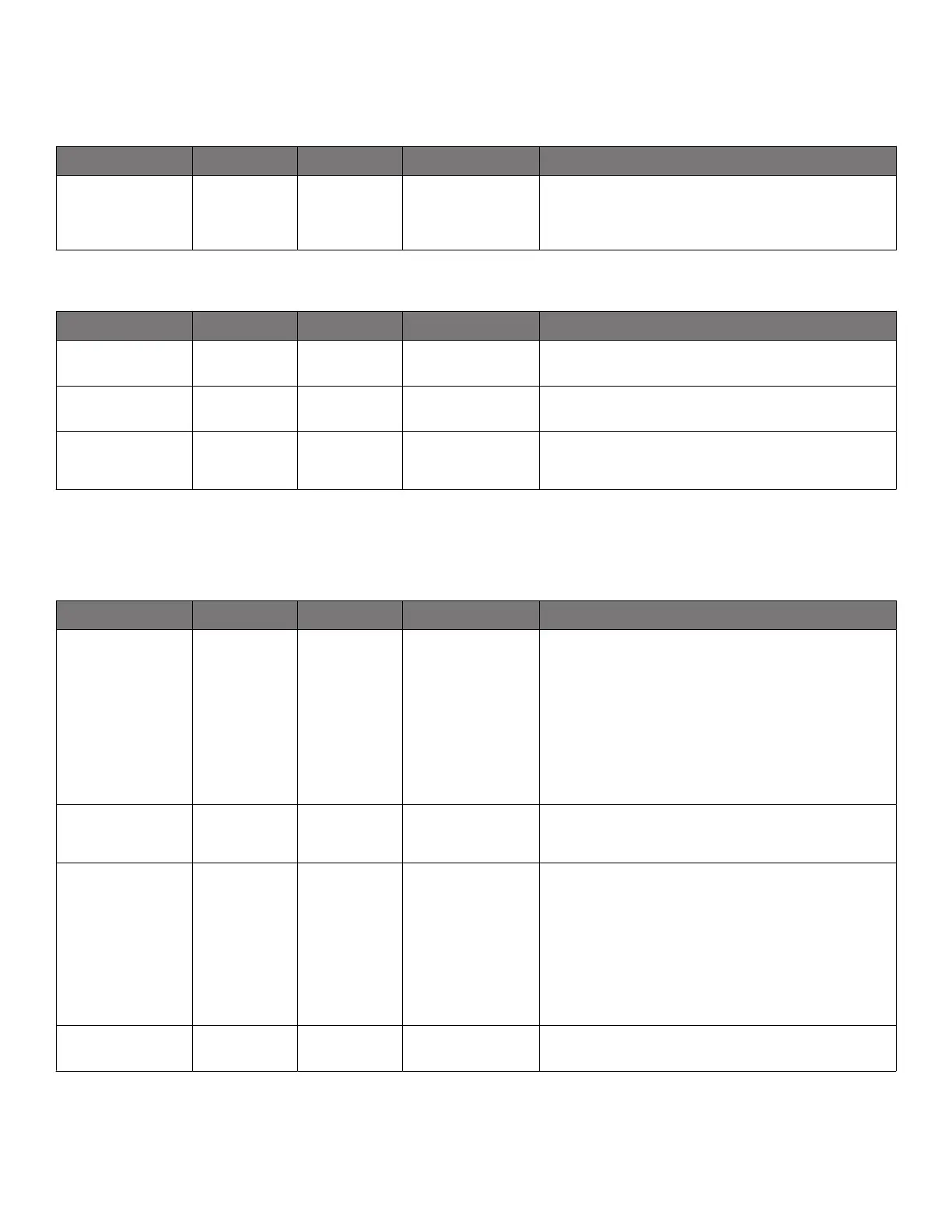

Table 14.132. 0x0112 Clock Output Driver 0 Configs and Div2 Mode

Reg Address Bit Field Type Setting Name Description

0x0112 0 R/W OUT0_PDN Output driver 0: 0 to power up the driver, 1 to power

down the driver. Clock outputs will be weakly pulled-low.

0x0112 1 R/W OUT0_OE Output driver 0: 0 to disable the output, 1 to enable the

output

0x0112 2 R/W OUT0_RDIV_FORC

E2

0 R0 divider value is set by R0_REG

1 R0 divider value is forced into divide by 2

Setting R0_REG=0 will not set the divide value to divide-by-2 automatically. OUT0_RDIV_FORCE2 must be set to a value of 1

to force R0 to divide-by-2. Note that the R0_REG value will be ignored while OUT0_RDIV_FORCE2 = 1. See R0_REG registers,

0x0250-0x0252, for more information.

Table 14.133. 0x0113 Clock Output Driver 0 Format

Reg Address Bit Field Type Setting Name Description

0x0113 2:0 R/W OUT0_FORMAT 0 Reserved

1 normal differential

2 Low Power differential

3 reserved

4 LVCMOS

5–7 reserved

0x0113 3 R/W OUT0_SYNC_EN 0 disable

1 enable

0x0113 5:4 R/W OUT0_DIS_STATE Determines the state of an output driver when disabled,

selectable as

0 disable in low state

1 disable in high state

2 reserved

3 reserved

0x0113 7:6 R/W OUT0_CMOS_DRV LVCMOS output impedance. See 5.3.5 LVCMOS Out-

put Impedance and Drive Strength Selection .

Si5341, Si5340 Rev D Family Reference Manual • Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

94 Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 94

Loading...

Loading...