14.2.5 Page 9 Registers Si5341

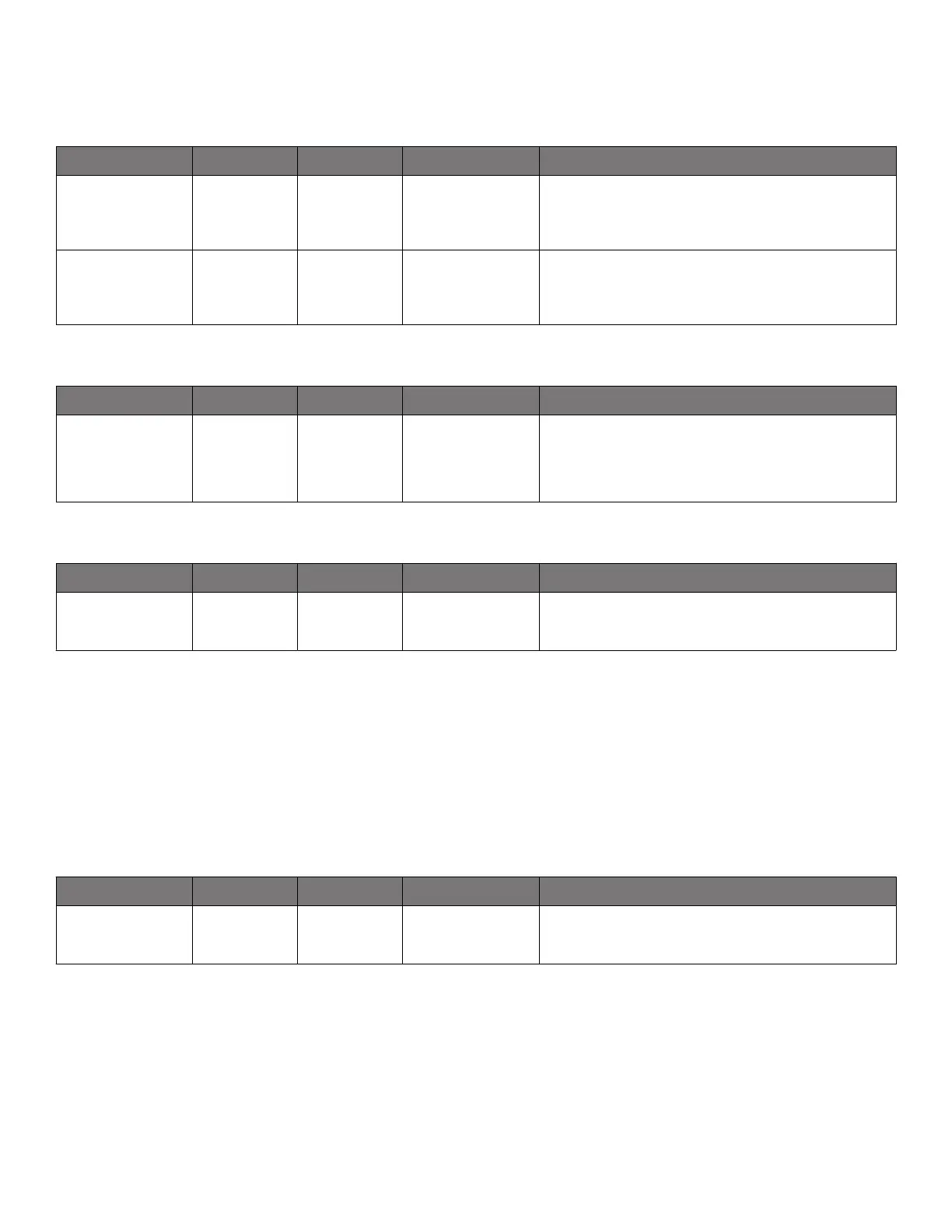

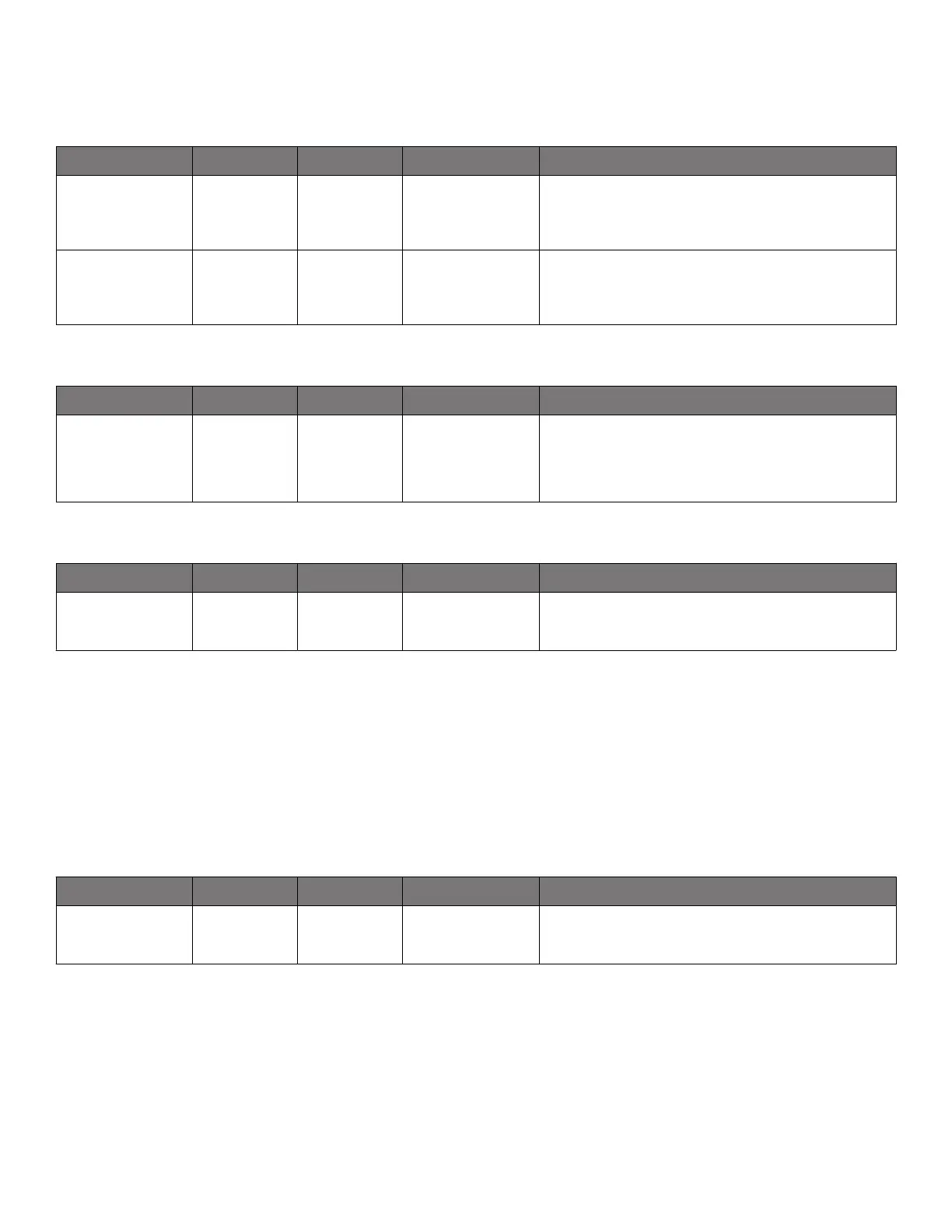

Table 14.81. 0x090E XAXB Configuration

Reg Address Bit Field Type Setting Name Description

0x090E 0 R/W XAXB_EXTCLK_EN 0 to use a crystal at the XAXB pins

1 to use an external clock source at the XAXB pins. A

singled ended clock must be applied at the XA input.

0x090E 1 R/W XAXB_PDNB 0-Power down the oscillator and buffer circuitry at the

XA/XB pins

1- No power down

Table 14.82. 0x091C Enable Zero Delay Mode

Reg Address Bit Field Type Setting Name Description

0x091C 2:0 R/W ZDM_EN 3 = Zero delay mode.

4 = Normal mode.

All other values must not be written.

Table 14.83. 0x0943 Status and Control I/O Voltage Select

Reg Address Bit Field Type Setting Name Description

0x0943 0 R/W IO_VDD_SEL 0 for 1.8 V external connections

1 for 3.3 V external connections

The IO_VDD_SEL configuration bit selects the option of operating the serial interface voltage thresholds from the VDD or the VDDA

pin. By default the IO_VDD_SEL bit is set to the VDD option. The serial interface pins are always 3.3 V tolerant even when the device's

VDD pin is supplied from a 1.8 V source. When the I

2

C or SPI host is operating at 3.3 V and the Si5341/40 IO_VDD_SEL = 1.8 V,

the host should write the IO_VDD_SEL configuration bit to the VDDA option. This will ensure that both the host and the serial interface

are operating at the optimum voltage thresholds. The IO_VDD_SEL bit also affects the status pin levels and control pin thresholds.

When IO_VDD_SEL = 0, the status outputs will have a VOH of ~1.8 V. When IO_VDD_SEL = 1 the status outputs will have a VOH of

~3.3 V. When IO_VDD_SEL=0, the control input pins will have an input threshold based upon the VDD supply voltage of 1.8 V. When

IO_VDD_SEL=1, the control input pins will have an input threshold based upon the VDDA supply voltage of 3.3 V. See Table 4 and

Table 6 of the Si5341/40 data sheet for details.

Table 14.84. 0x0949 Clock Input Control

Reg Address Bit Field Type Setting Name Description

0x0949 3:0 R/W IN_EN Enables for the four inputs clocks, IN0 through FB_IN.

1 to enable, 0 to disable

• Input 0 corresponds to IN_EN 0x0949 [0].

• Input 1 corresponds to IN_EN 0x0949 [1].

• Input 2 corresponds to IN_EN 0x0949 [2].

• FB_IN corresponds to IN_EN 0x0949 [3].

Si5341, Si5340 Rev D Family Reference Manual • Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

82 Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 82

Loading...

Loading...