14.2.7 Page B Registers Si5341

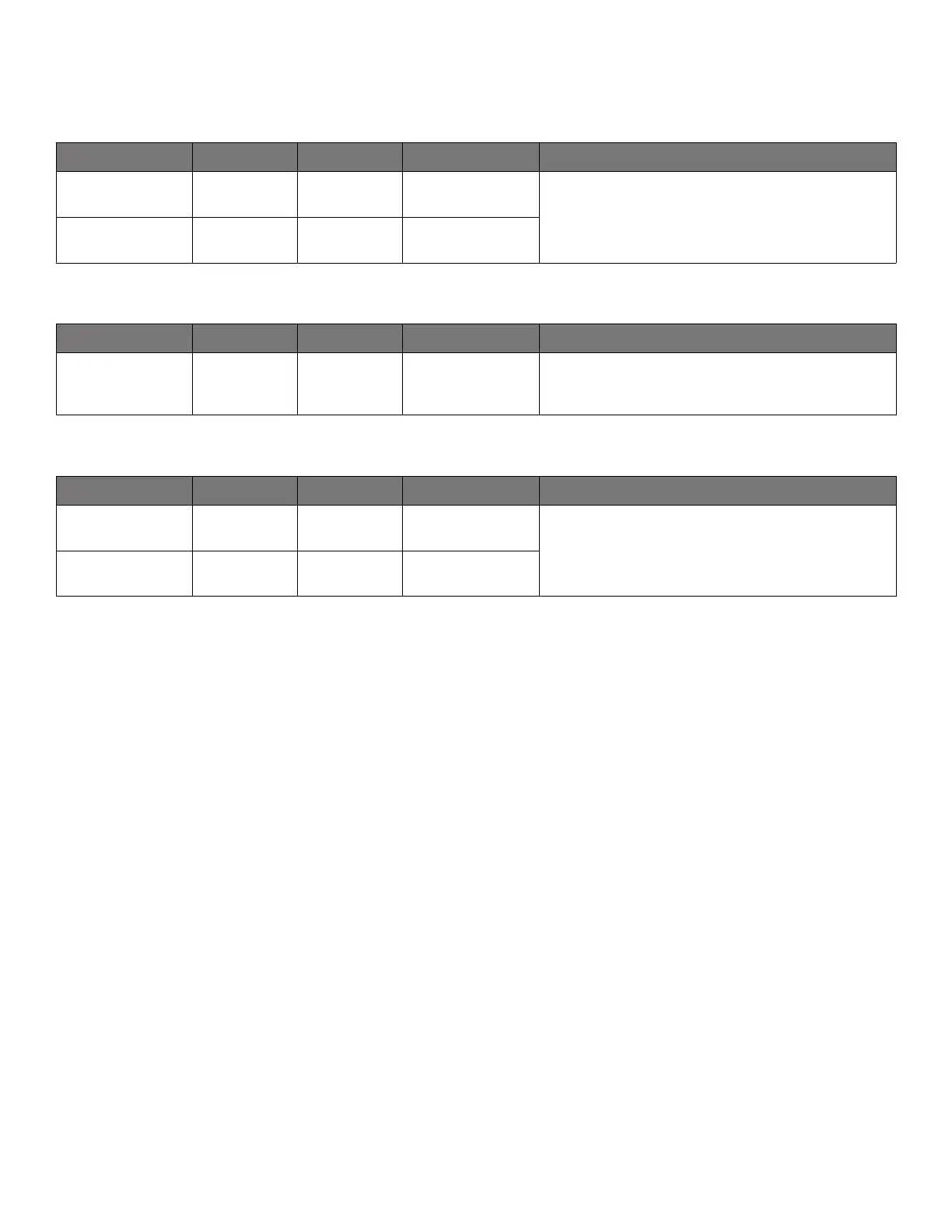

Table 14.90. 0x0B2E Synchronous Output Disable Timeout Value

Reg Address Bit Field Type Setting Name Description

0x0B2E 6:0 R/W MS_OD_G_TIME-

OUT

Controls the synchronous output disable timeout value

during a hard reset.

0x0B2E 7 R/W MS_OD_G_TIME-

OUT_EN

Table 14.91. 0x0B4A Divider Clock Disables

Reg Address Bit Field Type Setting Name Description

0x0B4A 4:0 R/W N_CLK_DIS Controls the clock to the N divider. If an N divider is

used the corresponding bit must be 0. [N3 N2 N1 N0].

See also registers 0x0A03 and 0x0A05.

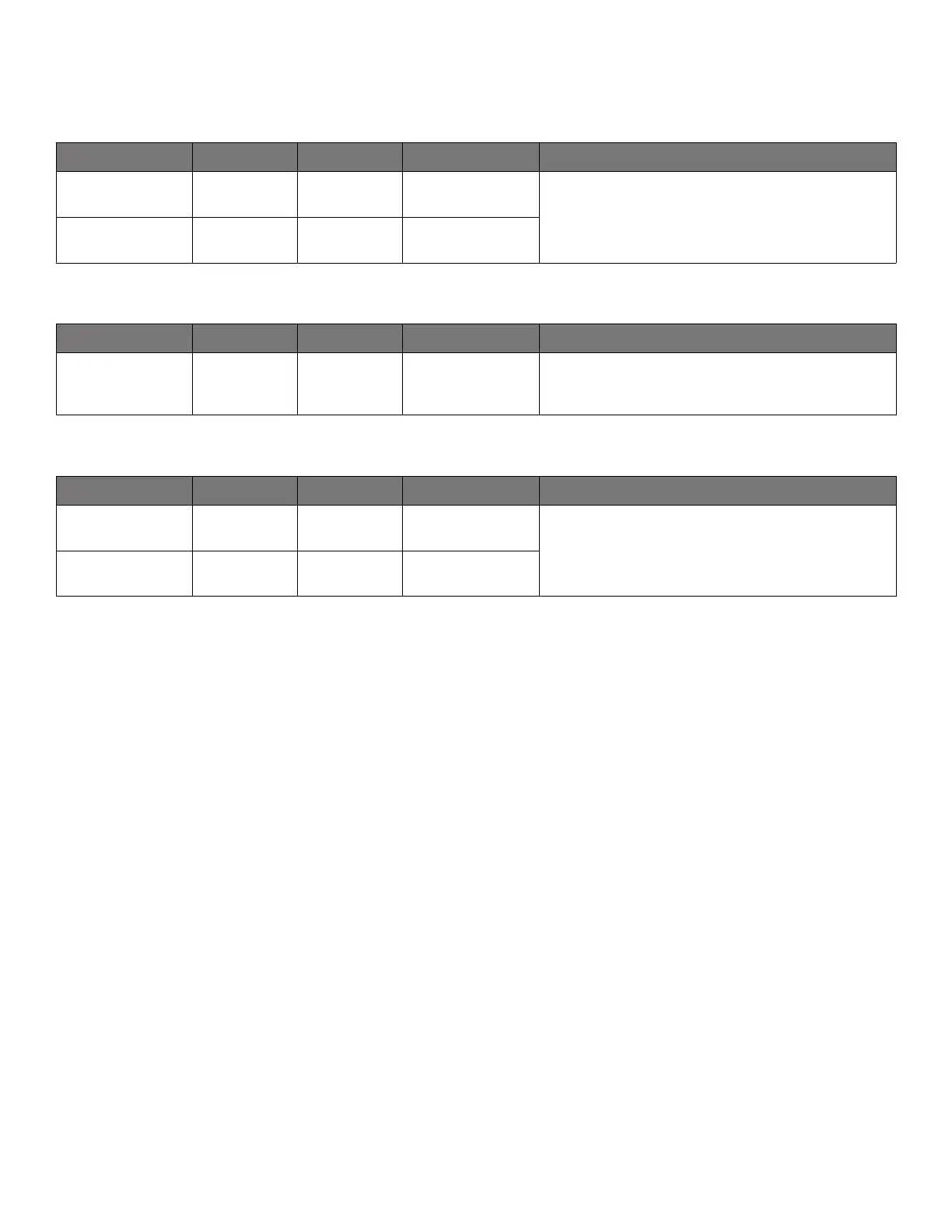

Table 14.92. 0x0B57

Reg Address Bit Field Type Name Description

0x0B57 7:0 R/W VCO_RESET_CAL-

CODE

12-bit value

0x0B58 11:8 R/W VCO_RESET_CAL-

CODE

14.3 Si5340 Registers

Because preprogrammed devices are inherently quite different from one another, the default power up values of the registers can be

determined using the Custom OPN Utility. Some registers that are listed in the Data Sheet Addendum are not documented in the

Register Map below because they are set and maintained by Clock Builder Pro. In almost all circumstances, these registers should not

be modified by the user. For more details, contact Silicon Labs technical support.

Si5341, Si5340 Rev D Family Reference Manual • Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

84 Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 84

Loading...

Loading...