35

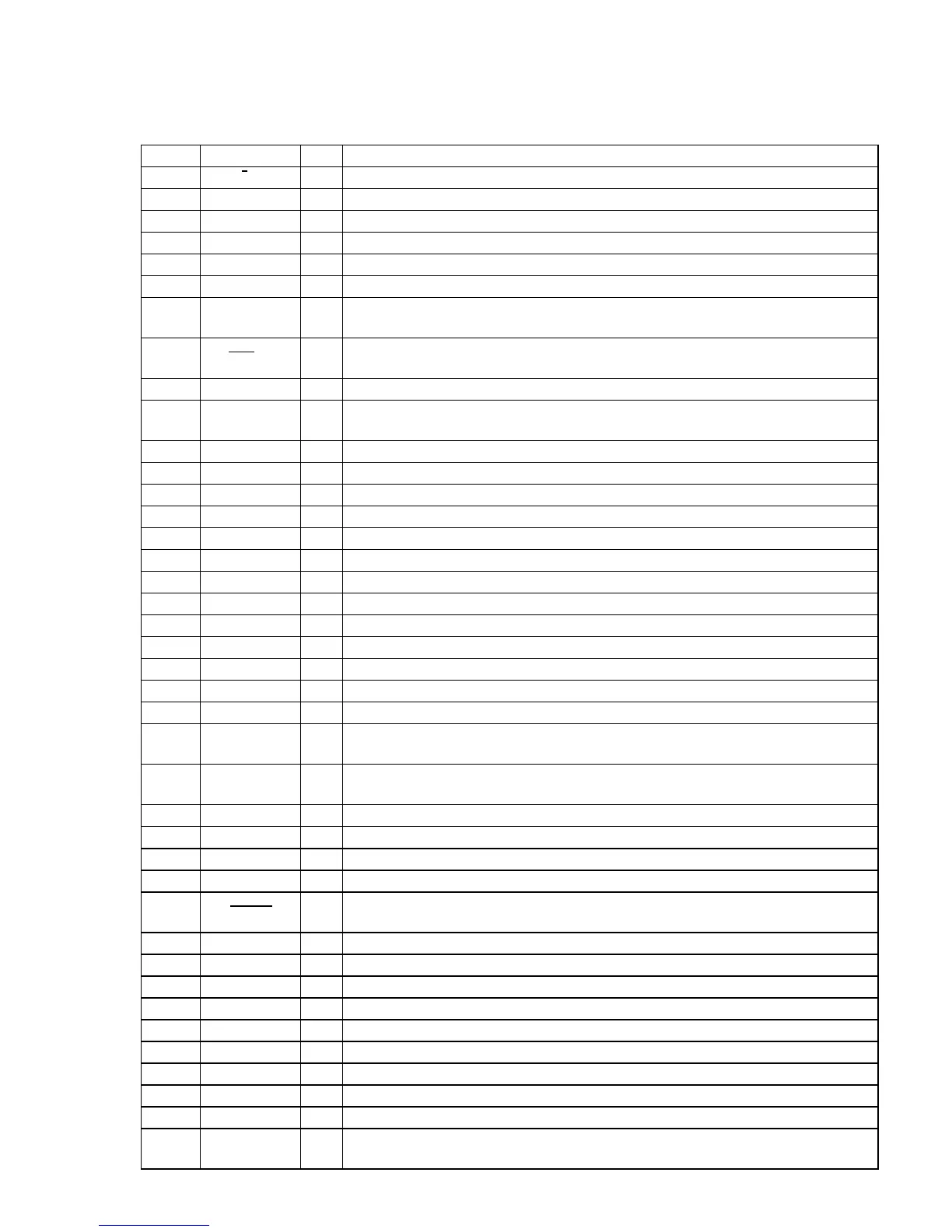

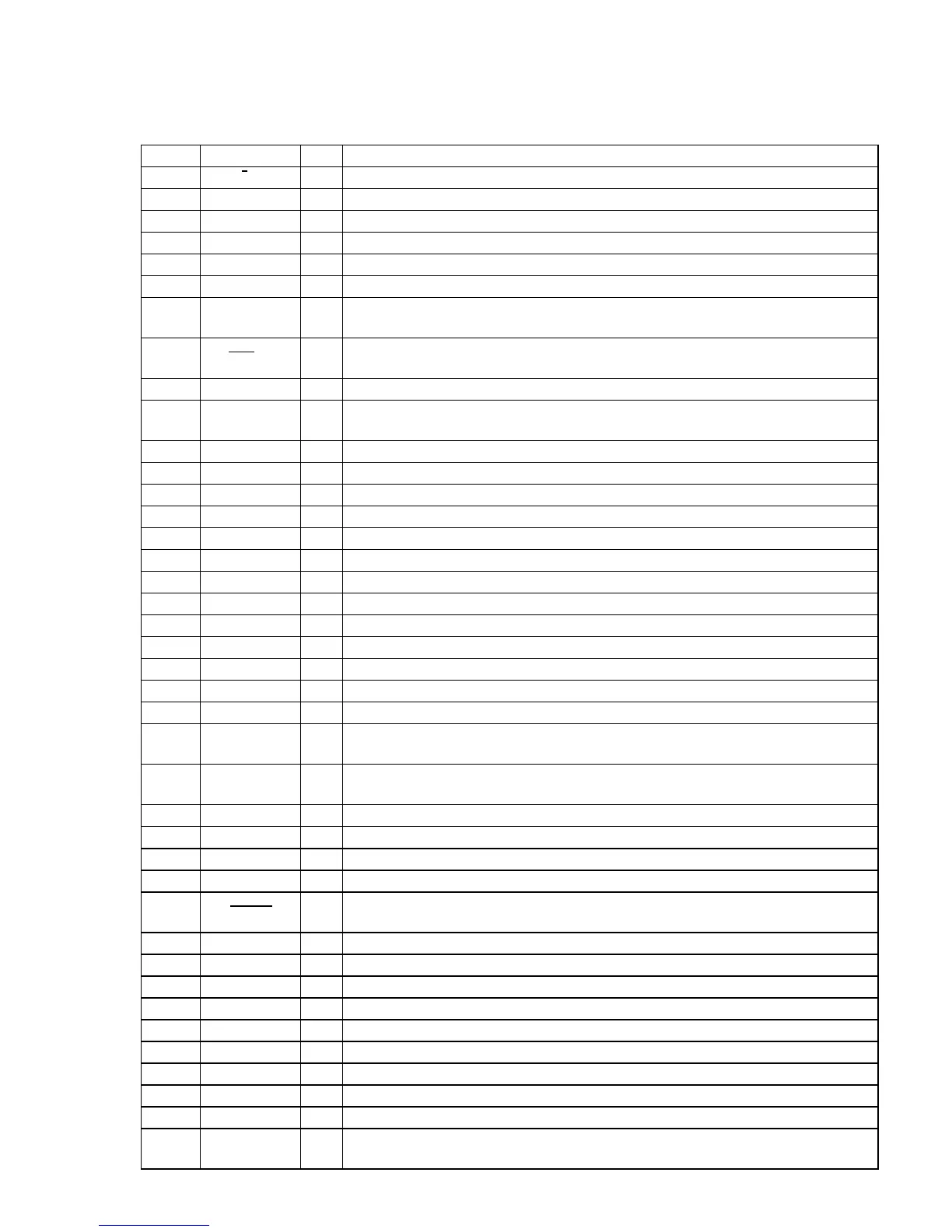

7-18. IC PIN FUNCTION DESCRIPTION

• MAIN BOARD IC802 CXP84332-224Q (SYSTEM CONTROLLER)

Pin No. Pin Name I/O Description

1 A/B O Deck-A/B selection signal output to the HA12215F (IC306) “L”: deck-A, “H”: deck-B

2 TREBLE A I Jog dial pulse input from the rotary encoder (RV803 TREBLE) (A phase input)

3

REC (DUB/HI-DUB)

O High speed dubbing control signal output to the HA12215F (IC306)

4 C-XRST O Reset signal output to the CXD2587Q (IC101) and BA5974FP (IC102) “L”: reset

5 AMP-S/B O Standby on/off control signal output to the power amplifier (IC101, 201) “L”: standby mode

6 AMP-MUTE O Muting on/off control signal output to the power amplifier (IC101, 201) “H”: muting on

7 REC-BIAS O

Recording bias on/off selection signal output to the HA12215F (IC306)

“L”: bias on, “H”: bias off

8 REC/PB O

Recording/playback/pass selection signal output to the HA12215F (IC306)

“L”: recording mode, “H”: playback mode

9

CAP-MOTOR-CON

O Capstan motor on/off control signal output terminal “H”: motor on

10

CAP-MOTOR-H/L

O

High/normal speed selection signal output of the capstan motor

“L”: normal speed, “H”: high speed

11 TRIG CON (A) O Deck-A side trigger plunger on/off control signal output “H”: plunger on

12 TRIG CON (B) O Deck-B side trigger plunger on/off control signal output “H”: plunger on

13 BASE A I Jog dial pulse input from the rotary encoder (RV802 BASE) (A phase input)

14 T-HALF (A) I Detection input from the deck-A cassette detect switch “L”: cassette in, “H”: no cassette

15 T-PLAY (A) I Detection input from the deck-A play detect switch “H”: deck-A play

16 T-SHUT (A) I Shut off detection signal input from the deck-A side reel pulse detector

17 T-SHUT (B) I Shut off detection signal input from the deck-B side reel pulse detector

18 T-PLAY (B) I Detection input from the deck-B play detect switch “H”: deck-B play

19 TU-TUNED I Tuning detection signal input from the tuner pack “L”: tuned

20 TU-DATA O PLL serial data output to the tuner pack

21 TU-CLK O PLL serial data transfer clock signal output to the tuner pack

22 TU-COUNT I PLL serial data input from the tuner pack

23 TU-CE O PLL chip enable signal output to the tuner pack

24 RDS-DATA I

RDS serial data input from the RDS decoder (IC803)

(Used for the AEP, UK and North European models only)

25 RDS-ON O

Power supply on/off control signal output of the tuner pack (+7V) and RDS decoder (IC803)

(Used for the AEP, UK and North European models only)

26 C/D O Command data output to the liquid crystal display driver (IC800)

27 LCD DATA O Serial data output to the liquid crystal display driver (IC800)

28 LCD CLK O Serial data transfer clock signal output to the liquid crystal display driver (IC800)

29 LCD CE O Chip enable signal output to the liquid crystal display driver (IC800)

30 RESET I

System reset signal input from the reset signal generator (IC801) “L”: reset

For several hundreds msec. after the power supply rises, “L” is input, then it changes to “H”

31 EXTAL1 I Main system clock input terminal (4.19 MHz)

32 XTAL1 O Main system clock output terminal (4.19 MHz)

33 VSS — Ground terminal

34 TX O Sub system clock output terminal (32.768 kHz)

35 TEX I Sub system clock input terminal (32.768 kHz)

36 AVSS — Ground terminal (for A/D converter)

37 AVREF I Reference voltage (+5V) input terminal (for A/D converter)

38 SIMUKE I Destination setting terminal (A/D input)

39 B-HALF I Detection input from the deck-B half detect switch “L”: cassette in, “H”: no cassette

40 KEY1 I

Key input terminal (A/D input)

S800 to S807 (TUNING –/+, REC z, TAPE B M/m/x/Y, TUNER BAND keys input)

Loading...

Loading...