AN3320 Power supplies

Doc ID 18267 Rev 2 11/29

1.3.3 System reset

A system reset sets all registers to their reset values except for the reset flags in the clock

controller CSR register and the registers in the Backup domain (see Figure 1).

A system reset is generated when one of the following events occurs:

1. A low level on the NRST pin (external reset)

2. window watchdog end-of-count condition (WWDG reset)

3. Independent watchdog end-of-count condition (IWDG reset)

4. A software reset (SW reset)

5. Low-power management reset

The reset source can be identified by checking the reset flags in the Control/Status register,

RCC_CSR.

The STM32F20xxx/21xxx does not require an external reset circuit to power-up correctly.

Only a pull-down capacitor is recommended to improve EMS performance by protecting the

device against parasitic resets. See Figure 5.

Charging and discharging a pull-down capacitor through an internal resistor increases the

device power consumption. The capacitor recommended value (100 nF) can be reduced to

10 nF to limit this power consumption;

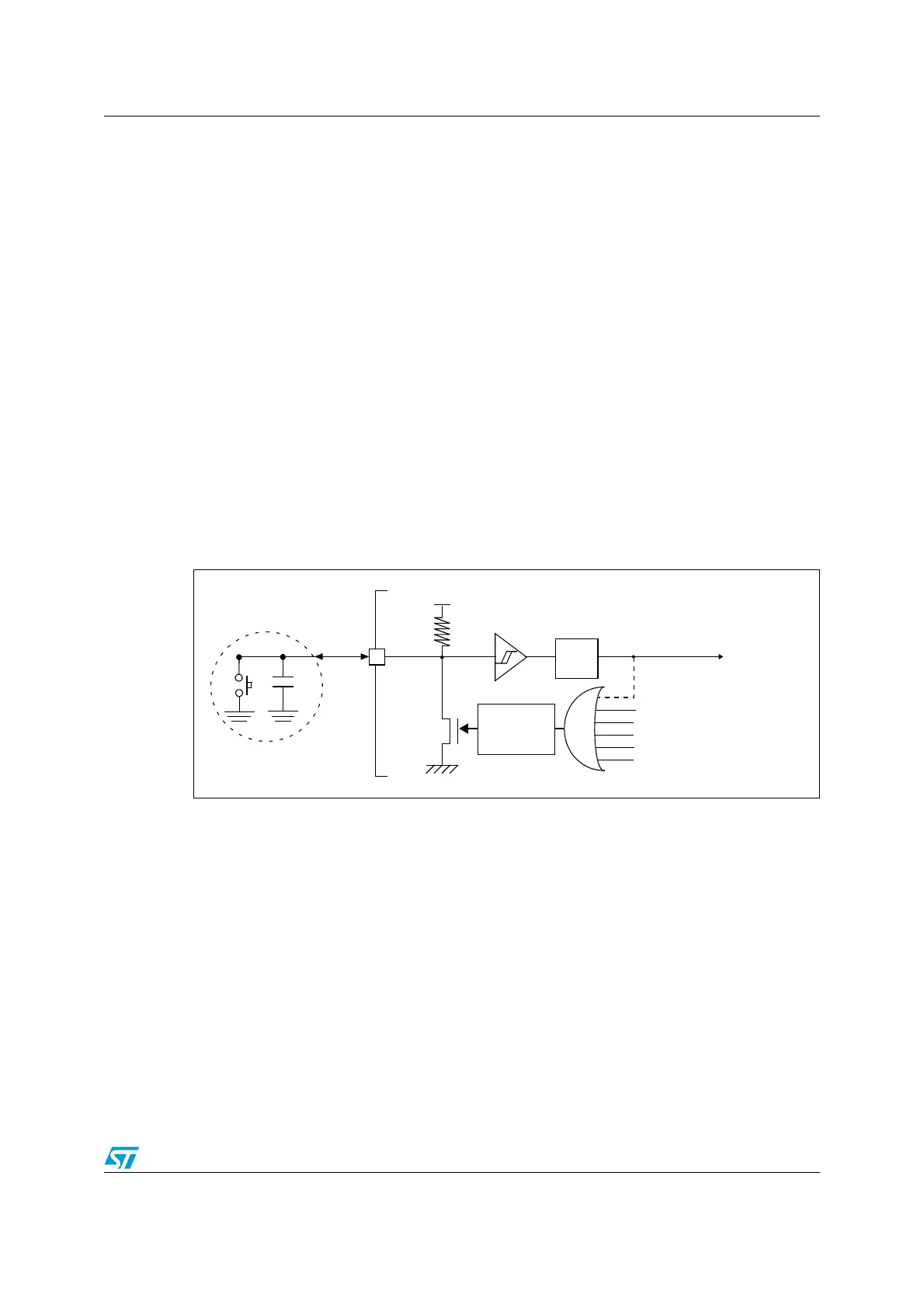

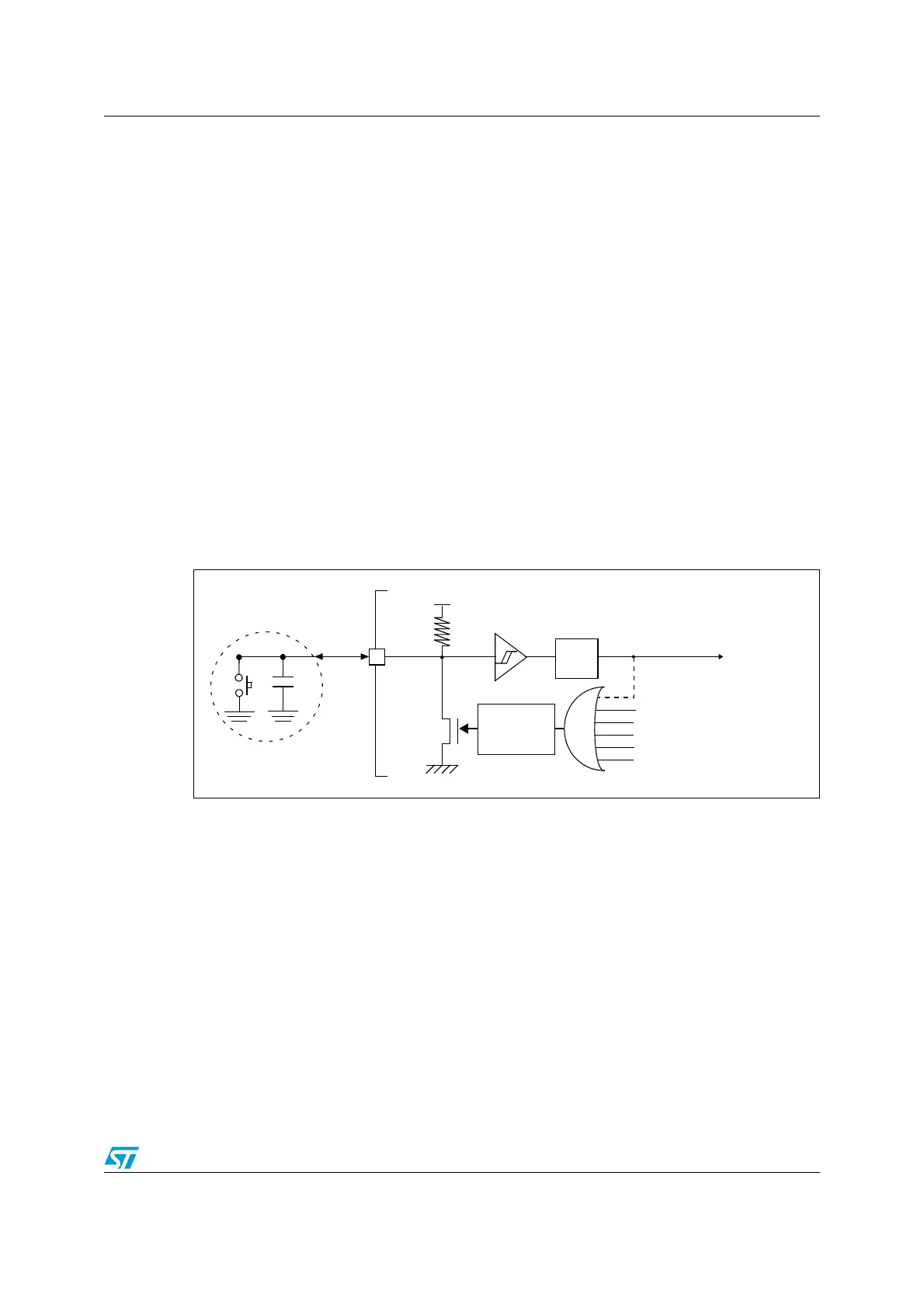

Figure 5. Reset circuit

2

05

6

$$

77$'RESET

)7$'RESET

0ULSE

GENERATOR

0OWERRESET

MINS

3YSTEMRESET

&ILTER

3OFTWARERESET

,OWPOWERMANAGEMENTRESET

&

%XTERNAL

RESETCIRCUIT

.234

!)

Loading...

Loading...