Debug management AN3320

20/29 Doc ID 18267 Rev 2

To avoid any uncontrolled I/O levels, the STM32F20xxx/21xxx embeds internal pull-up and

pull-down resistors on JTAG input pins:

● JNTRST: Internal pull-up

● JTDI: Internal pull-up

● JTMS/SWDIO: Internal pull-up

● TCK/SWCLK: Internal pull-down

Once a JTAG I/O is released by the user software, the GPIO controller takes control again.

The reset states of the GPIO control registers put the I/Os in the equivalent state:

● JNTRST: Input pull-up

● JTDI: Input pull-up

● JTMS/SWDIO: Input pull-up

● JTCK/SWCLK: Input pull-down

● JTDO: Input floating

The software can then use these I/Os as standard GPIOs.

Note: The JTAG IEEE standard recommends to add pull-up resistors on TDI, TMS and nTRST but

there is no special recommendation for TCK. However, for the STM32F20xxx/21xxx, an

integrated pull-down resistor is used for JTCK.

Having embedded pull-up and pull-down resistors removes the need to add external

resistors.

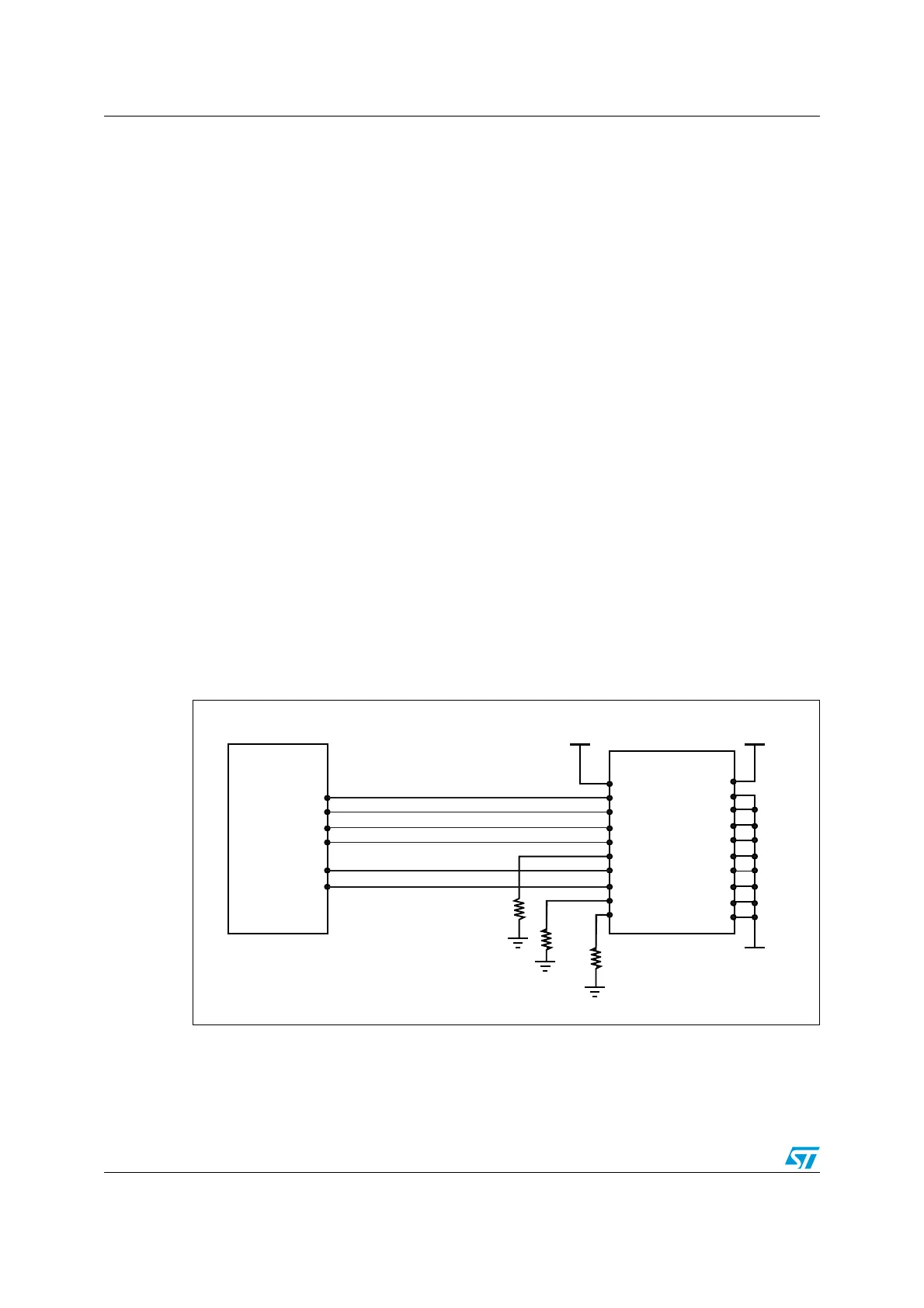

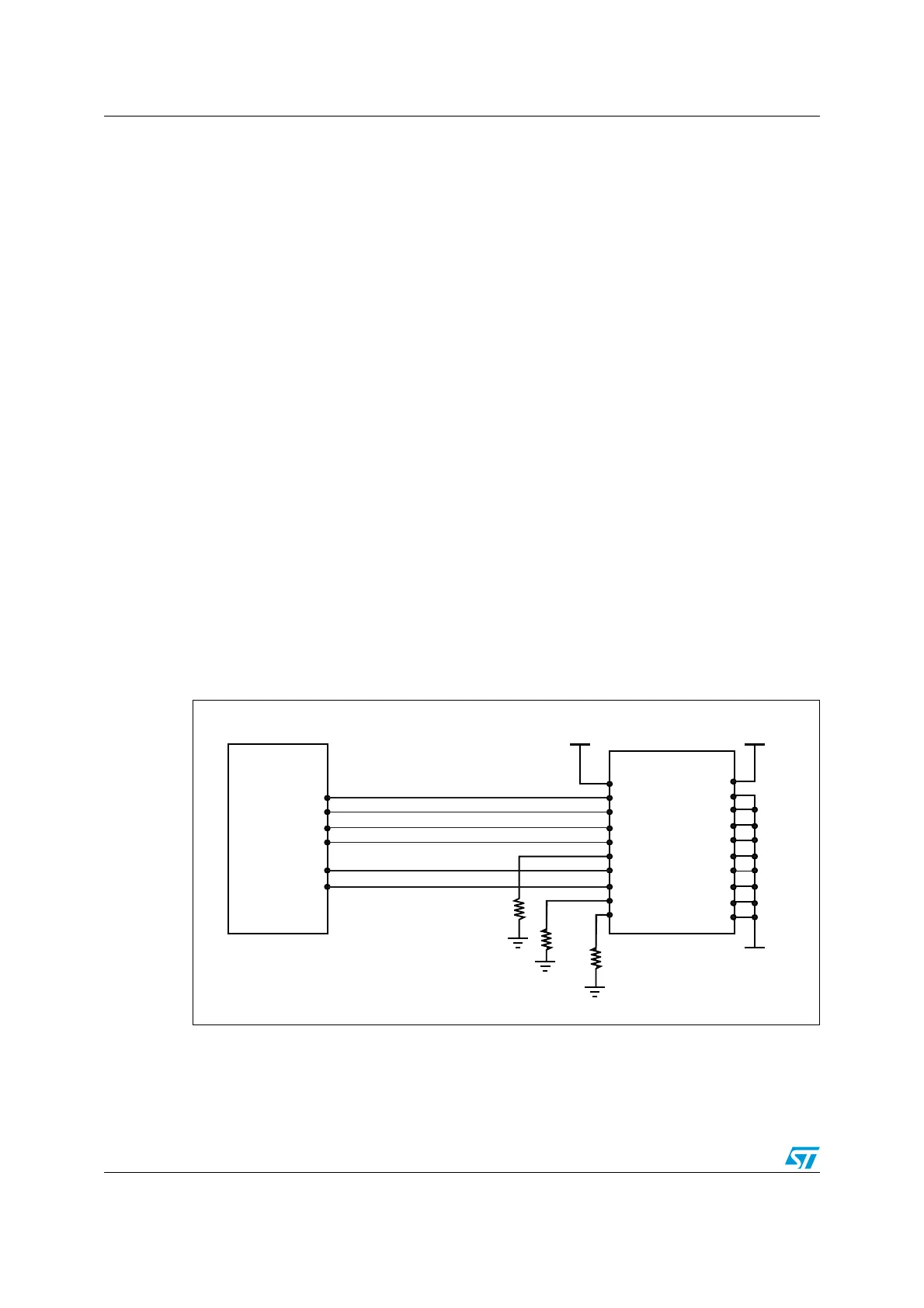

4.3.4 SWJ debug port connection with standard JTAG connector

Figure 12 shows the connection between the STM32F20xxx/21xxx and a standard JTAG

connector.

Figure 12. JTAG connector implementation

AIB

6

$$

6

$$

34-&

N*4234

*4$)

*34-37$)/

*4#+37#,+

*4$/

N234).

642%&

N4234

4$)

4-3

4#+

24#+

4$/

N3234

$"'21

$"'!#+

KΩ

KΩ

KΩ

6

33

#ONNECTOR§

*4!'CONNECTOR#.

Loading...

Loading...