RM0440 Rev 4 1067/2126

RM0440 High-resolution timer (HRTIM)

1083

27.5.77 HRTIM ADC trigger update register (HRTIM_ADCUR)

Address offset: 0x3FC

Reset value: 0x0000 0000

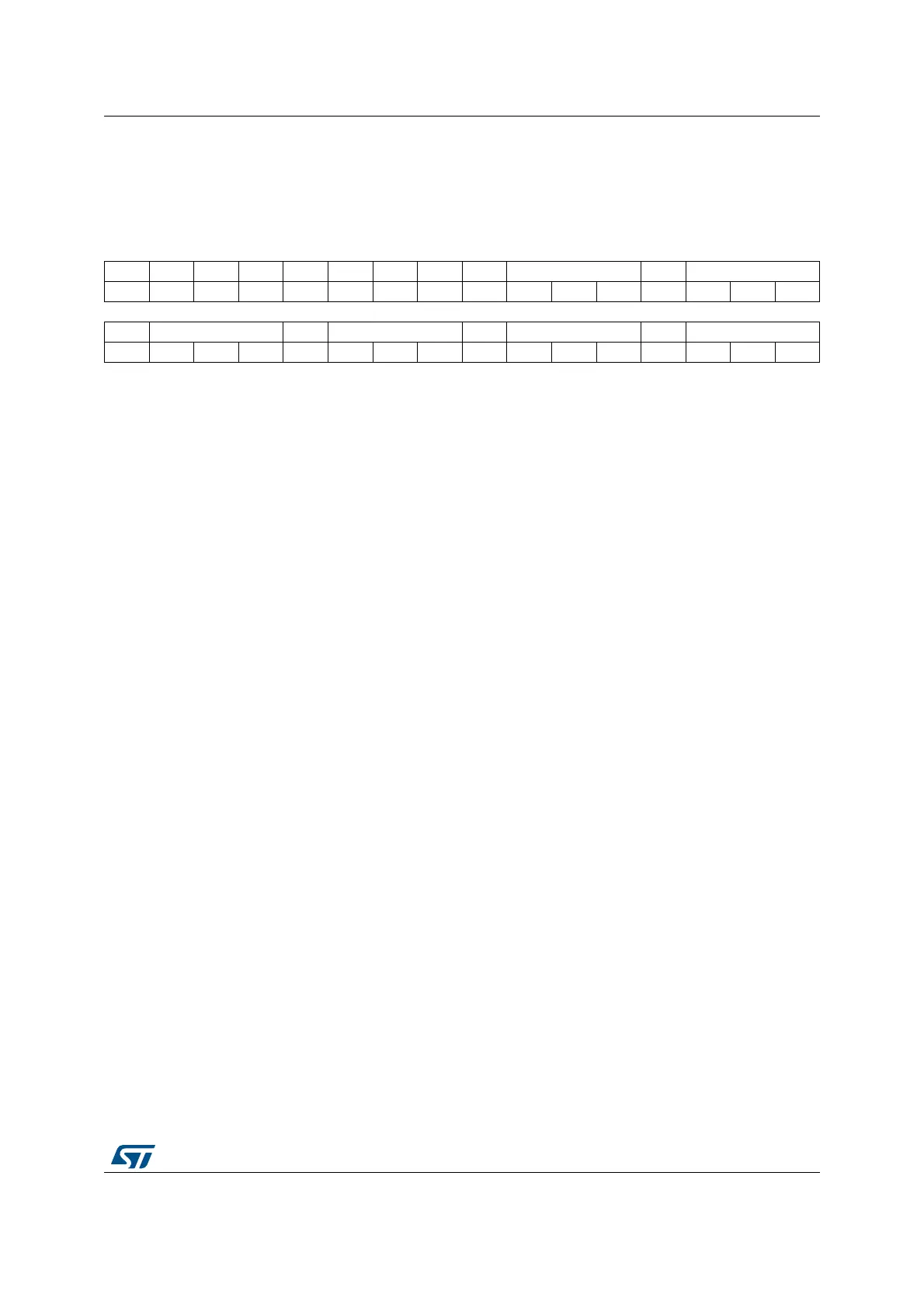

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. AD10USRC[2:0] Res. AD9USRC[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

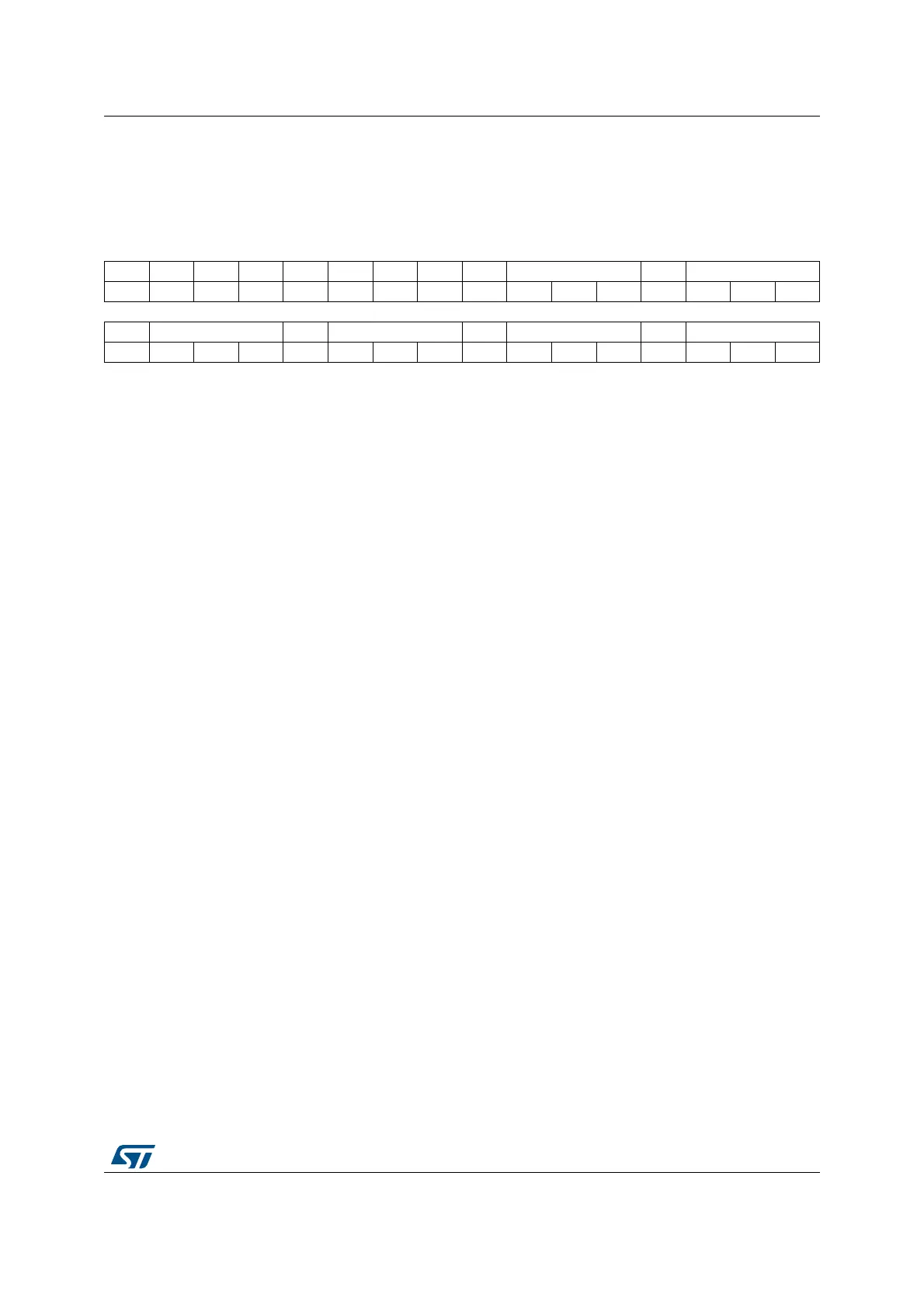

1514131211109876543210

Res. AD8USRC[2:0] Res. AD7USRC[2:0] Res. AD6USRC[2:0] Res. AD5USRC[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:23 Reserved, must be kept at reset value.

Bits 22:20 AD10USRC[2:0]: ADC trigger 10 update source

Refer to AD5USRC[2:0] description.

Bit 19 Reserved, must be kept at reset value.

Bits 18:16 AD9USRC[2:0]: ADC trigger 9 update source

Refer to AD5USRC[2:0] description.

Bit 15 Reserved, must be kept at reset value.

Bits 14:12 AD8USRC[2:0]: ADC trigger 8 update source

Refer to AD5USRC[2:0] description.

Bit 11 Reserved, must be kept at reset value.

Bits 10:8 AD7USRC[2:0]: ADC trigger 7 update source

Refer to AD5USRC[2:0] description.

Bit 7 Reserved, must be kept at reset value.

Bits 6:4 AD6USRC[2:0]: ADC trigger 6 update source

Refer to AD5USRC[2:0] description.

Bit 3 Reserved, must be kept at reset value.

Bits 2:0 AD5USRC[2:0]: ADC trigger 5 update source

These bits define the source which triggers the update of the ADC5TRG[4:0] bitfield in the

HRTIM_ADCER register (transfer from preload to active register). It only defines the source timer.

The precise condition is defined within the timer itself, with the BRSTDMA[1:0] bitfield in

HRTIM_MCR or the UPDGAT[3:0] bitfield in HRTIM_TIMxCR register.

000: Master timer

001: Timer A

010: Timer B

011: Timer C

100: Timer D

101: Timer E

110: Timer F

111: Reserved

Loading...

Loading...