Debug management AN3216

20/30 Doc ID 17496 Rev 5

5 Debug management

5.1 Introduction

The host/target interface is the hardware equipment that connects the host to the application

board. This interface is made of three components: a hardware debug tool, a JTAG or SW

connector and a cable connecting the host to the debug tool.

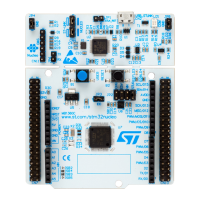

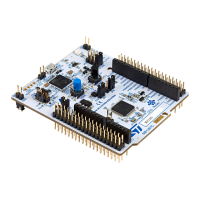

Figure 12 shows the connection of the host to a development board. The evaluation board

(STM32L152-EVAL) embeds the debug tools (ST-LINK) so it can be directly connected to

the PC through an USB cable.

Figure 12. Host-to-board connection

5.2 SWJ debug port (serial wire and JTAG)

The STM32L1xxx core integrates the serial wire/JTAG debug port (SWJ-DP). It is an ARM®

standard CoreSight™ debug port that combines a JTAG-DP (5-pin) interface and a SW-DP

(2-pin) interface.

● The JTAG debug port (JTAG-DP) provides a 5-pin standard JTAG interface to the AHP-

AP port

● The serial wire debug port (SW-DP) provides a 2-pin (clock + data) interface to the

AHP-AP port

In the SWJ-DP, the two JTAG pins of the SW-DP are multiplexed with some of the five JTAG

pins of the JTAG-DP.

5.3 Pinout and debug port pins

The STM32L1xxx MCU is offered in various packages with different numbers of available

pins. As a result, some functionality related to the pin availability may differ from one

package to another.

$EVELOPMENTBOARD

(OST0#

0OWERSUPPLY

*4!'37CONNECTOR

$EBUGTOOL

AIC