KCU105 Board User Guide www.xilinx.com 42

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

For additional information on GTH transceivers, see UltraScale Architecture GTH

Transceivers User Guide (UG576) [Ref 6] and UltraScale FPGAs Transceivers Wizard Product

Guide for Vivado Design Suite (PG182) [Ref 7]. For additional information about UltraScale

FPGA PCIe functionality, see UltraScale Architecture Gen3 Integrated Block for PCI Express

LogiCORE IP Product Guide (PG156) [Ref 8]. Additional information about the PCI Express

standard is available at the PCI Express website [Ref 29].

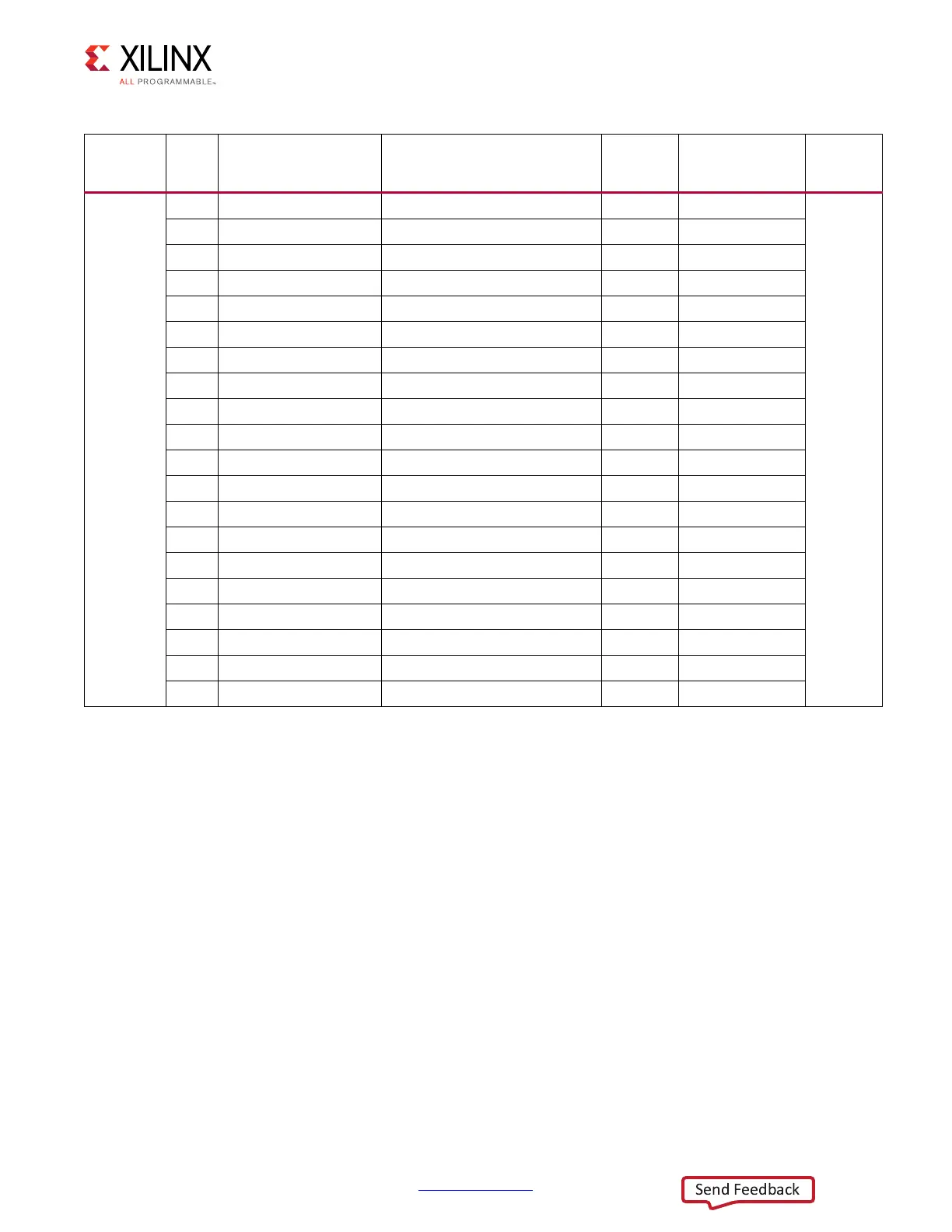

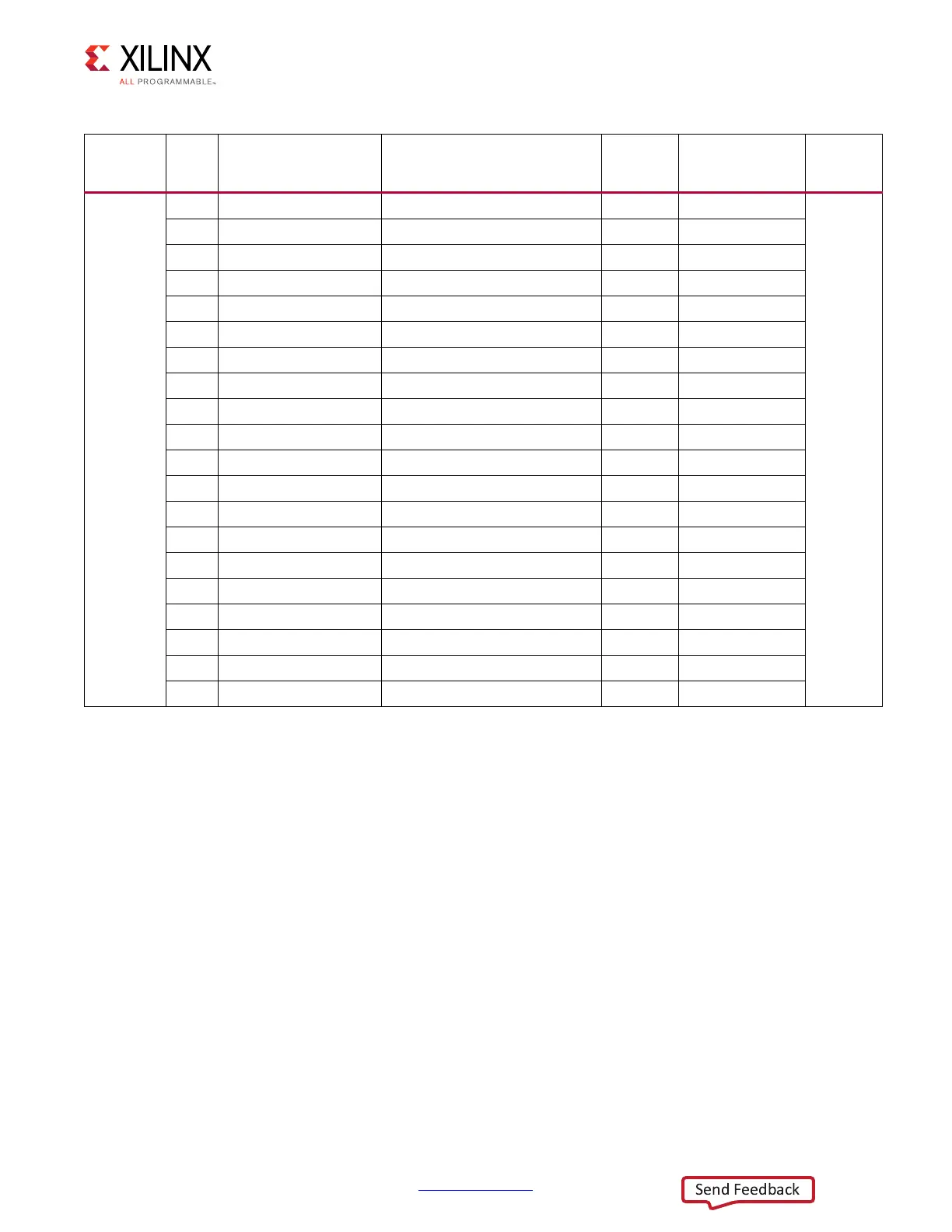

GTH Bank

228

F6 MGTHTXP0_228 FMC_HPC_DP0_C2M_P C2 DP0_C2M_P

FMC HPC

J22

F5 MGTHTXN0_228 FMC_HPC_DP0_C2M_N C3 DP0_C2M_N

E4 MGTHRXP0_228 FMC_HPC_DP0_M2C_P C6 DP0_M2C_P

E3 MGTHRXN0_228 FMC_HPC_DP0_M2C_N C7 DP0_M2C_N

D6 MGTHTXP1_228 FMC_HPC_DP1_C2M_P A22 DP1_C2M_P

D5 MGTHTXN1_228 FMC_HPC_DP1_C2M_N A23 DP1_C2M_N

D2 MGTHRXP1_228 FMC_HPC_DP1_M2C_P A2 DP1_M2C_P

D1 MGTHRXN1_228 FMC_HPC_DP1_M2C_N A3 DP1_M2C_N

C4 MGTHTXP2_228 FMC_HPC_DP2_C2M_P A26 DP2_C2M_P

C3 MGTHTXN2_228 FMC_HPC_DP2_C2M_N A27 DP2_C2M_N

B2 MGTHRXP2_228 FMC_HPC_DP2_M2C_P A6 DP2_M2C_P

B1 MGTHRXN2_228 FMC_HPC_DP2_M2C_N A7 DP2_M2C_N

B6 MGTHTXP3_228 FMC_HPC_DP3_C2M_P A30 DP3_C2M_P

B5 MGTHTXN3_228 FMC_HPC_DP3_C2M_N A31 DP3_C2M_N

A4 MGTHRXP3_228 FMC_HPC_DP3_M2C_P A10 DP3_M2C_P

A3 MGTHRXN3_228 FMC_HPC_DP3_M2C_N A11 DP3_M2C_N

K6 MGTREFCLK0P_228 FMC_HPC_GBTCLK0_M2C_C_P D4 GBTCLK0_M2C_P

K5 MGTREFCLK0N_228 FMC_HPC_GBTCLK0_M2C_C_N D5 GBTCLK0_M2C_N

H6 MGTREFCLK1P_228 FMC_HPC_GBTCLK1_M2C_C_P B20 GBTCLK1_M2C_P

H5 MGTREFCLK1N_228 FMC_HPC_GBTCLK1_M2C_C_N B21 GBTCLK1_M2C_N

Table 1-11: KCU105 Board FPGA U1 GTH Bank 227 and 228 Connections (Cont’d)

Transceiver

Bank

FPGA

(U1)

Pin

FPGA (U1) Pin Name Schematic Net Name

Connected

Pin

Connected Pin

Name

Connected

Device

Loading...

Loading...