KCU105 Board User Guide www.xilinx.com 41

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

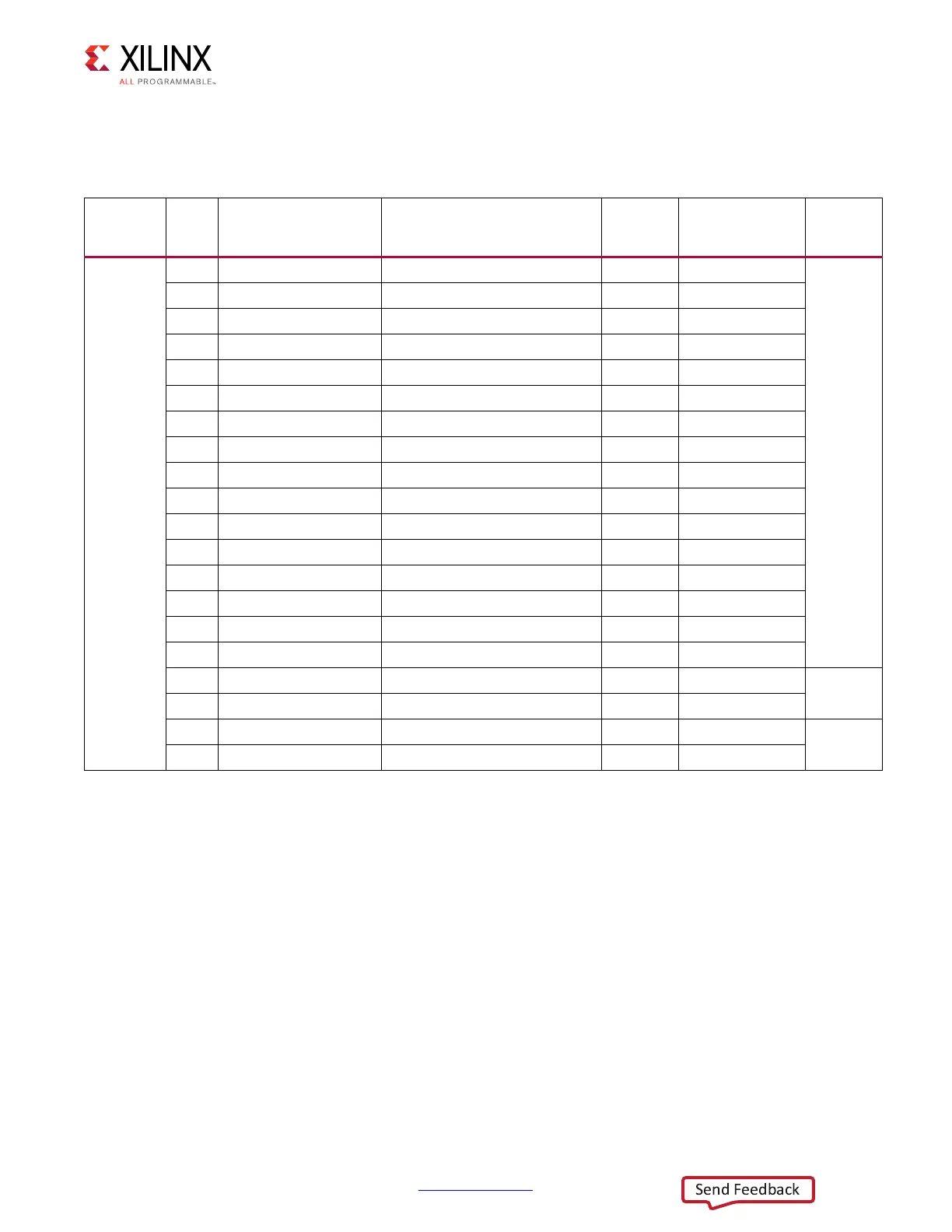

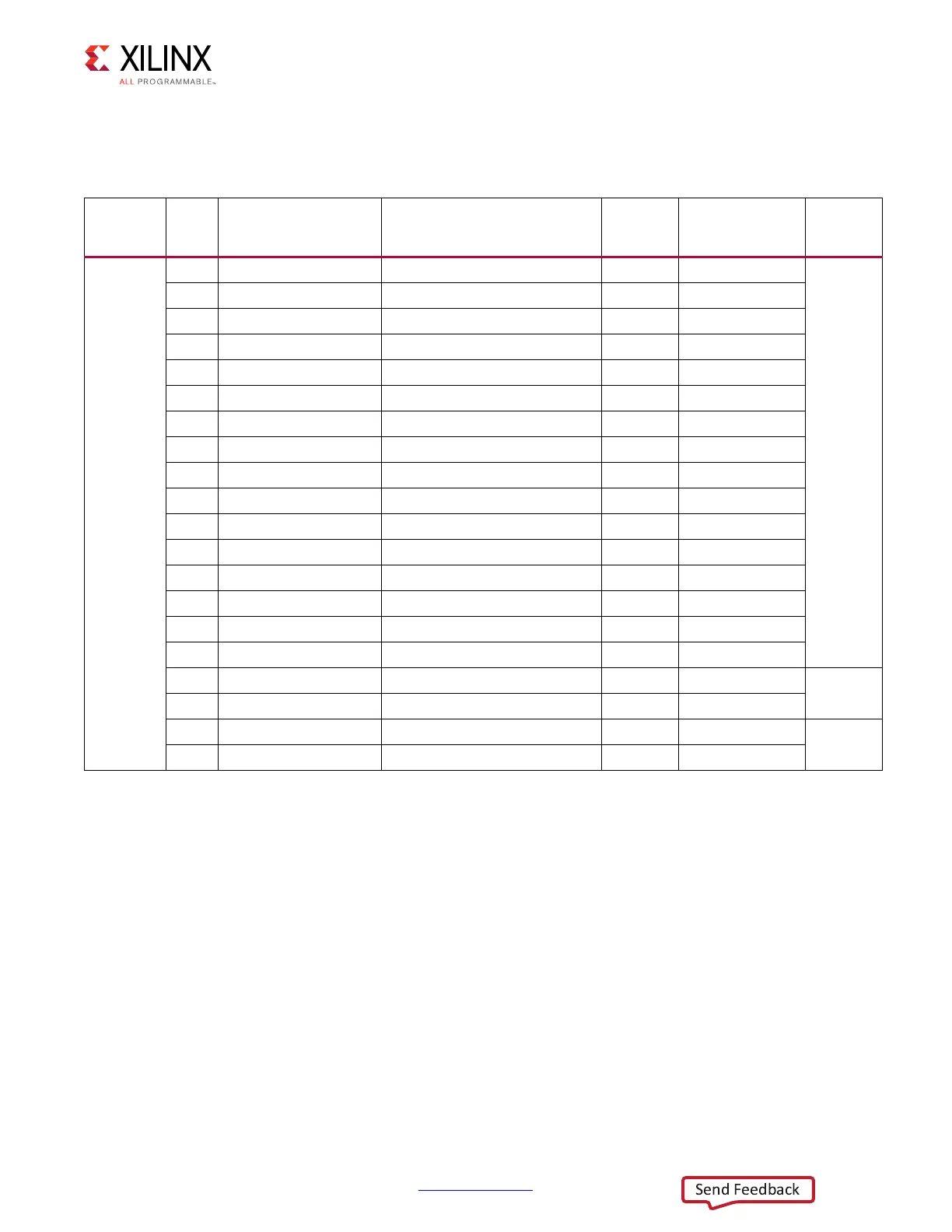

Tab le 1- 11 lists the GTH banks 227 and 228 interface connections between FPGA U1 and the

FMC HPC J22 connector.

Table 1-11: KCU105 Board FPGA U1 GTH Bank 227 and 228 Connections

Transceiver

Bank

FPGA

(U1)

Pin

FPGA (U1) Pin Name Schematic Net Name

Connected

Pin

Connected Pin

Name

Connected

Device

GTH Bank

227

N4 MGTHTXP0_227 FMC_HPC_DP4_C2M_P A34 DP4_C2M_N

FMC HPC

J22

N3 MGTHTXN0_227 FMC_HPC_DP4_C2M_N A35 DP4_C2M_P

M2 MGTHRXP0_227 FMC_HPC_DP4_M2C_P A14 DP4_M2C_P

M1 MGTHRXN0_227 FMC_HPC_DP4_M2C_N A15 DP4_M2C_N

L4 MGTHTXP1_227 FMC_HPC_DP6_C2M_P B36 DP6_C2M_P

L3 MGTHTXN1_227 FMC_HPC_DP6_C2M_N B37 DP6_C2M_N

K2 MGTHRXP1_227 FMC_HPC_DP6_M2C_P B16 DP7_C2M_P

K1 MGTHRXN1_227 FMC_HPC_DP6_M2C_N B17 DP7_C2M_N

J4 MGTHTXP2_227 FMC_HPC_DP5_C2M_P A38 DP5_C2M_P

J3 MGTHTXN2_227 FMC_HPC_DP5_C2M_N A39 DP5_C2M_N

H2 MGTHRXP2_227 FMC_HPC_DP5_M2C_P A18 DP5_M2C_P

H1 MGTHRXN2_227 FMC_HPC_DP5_M2C_N A19 DP5_M2C_N

G4 MGTHTXP3_227 FMC_HPC_DP7_C2M_P B32 DP6_M2C_P

G3 MGTHTXN3_227 FMC_HPC_DP7_C2M_N B33 DP6_M2C_N

F2 MGTHRXP3_227 FMC_HPC_DP7_M2C_P B12 DP7_M2C_P

F1 MGTHRXN3_227 FMC_HPC_DP7_M2C_N B13 DP7_M2C_N

P6 MGTREFCLK0P_227 MGT_SI570_CLOCK_C_P 11 Q1_P

Si53340

U104

P5 MGTREFCLK0N_227 MGT_SI570_CLOCK_C_N 12 Q1_N

M6 MGTREFCLK1P_227 SI5328_OUT_C_P 28 CKOUT1_P

Si5328B

U57

M5 MGTREFCLK1N_227 SI5328_OUT_C_N 29 CKOUT1_N

Loading...

Loading...