ABCDEFGH

1

2

3

4

5

6

IJKL

7

8

DSP-AX1/RX-V1

0

0

0

0.6

0.6

4.9

4.7

4.7

4.9

0.5

0.5

4.9

0.5

0.5

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0.6

0

0 0.5

0 0.5

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

-0.2

-0.1

-0.1

0

0

0

-0.1

0

-0.1

1.4

0

-0.2

-0.2

0.20.7

1.4

4.90.7

00

00

0

0

00

0

4.9

4.9

0

0

-4.9

0

0

4.9

4.9

0

0

-4.9

0

0

4.9

4.9

0

0

-4.9

-4.9

0

0

4.8

-4.9

4.9

0

4.8

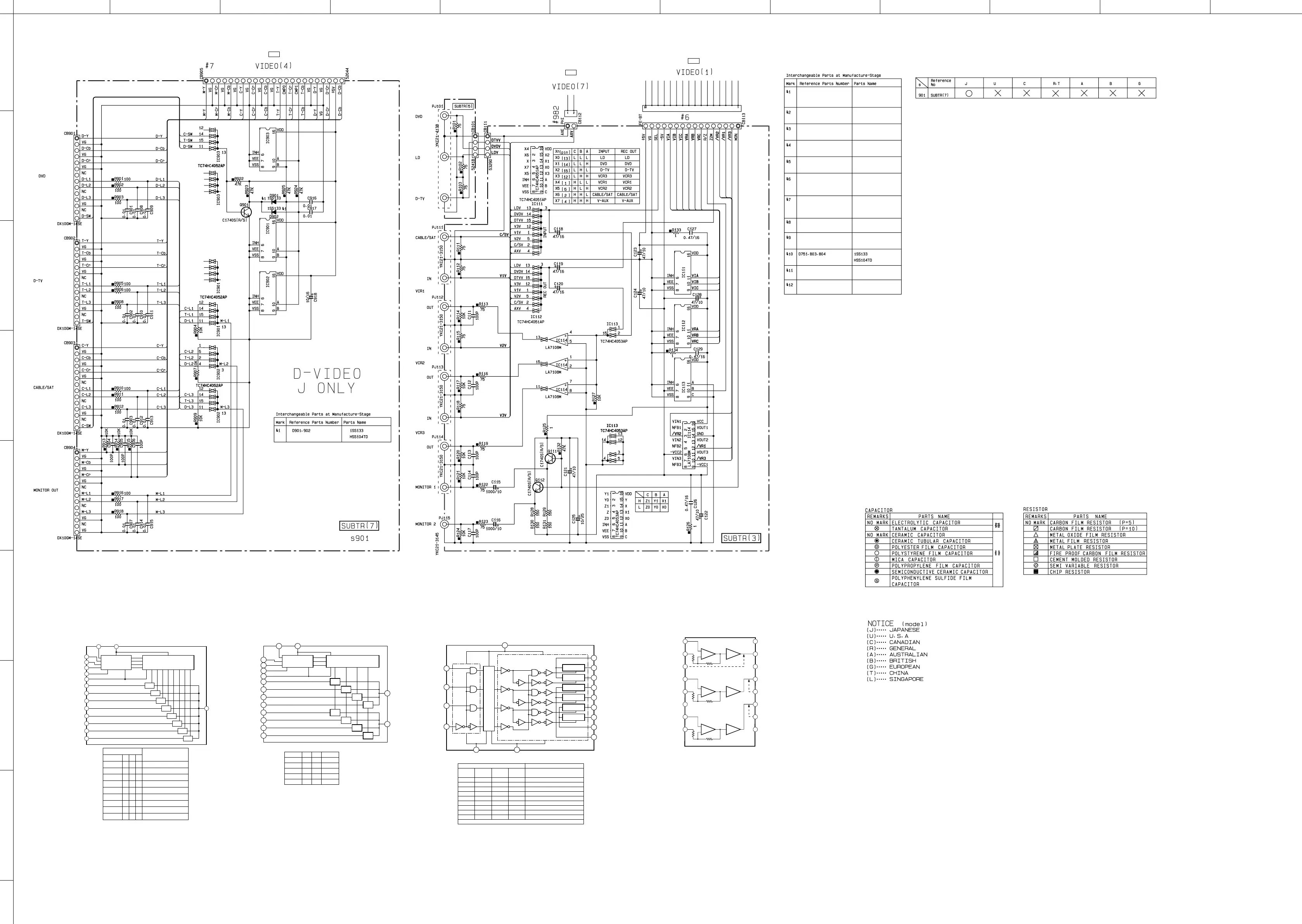

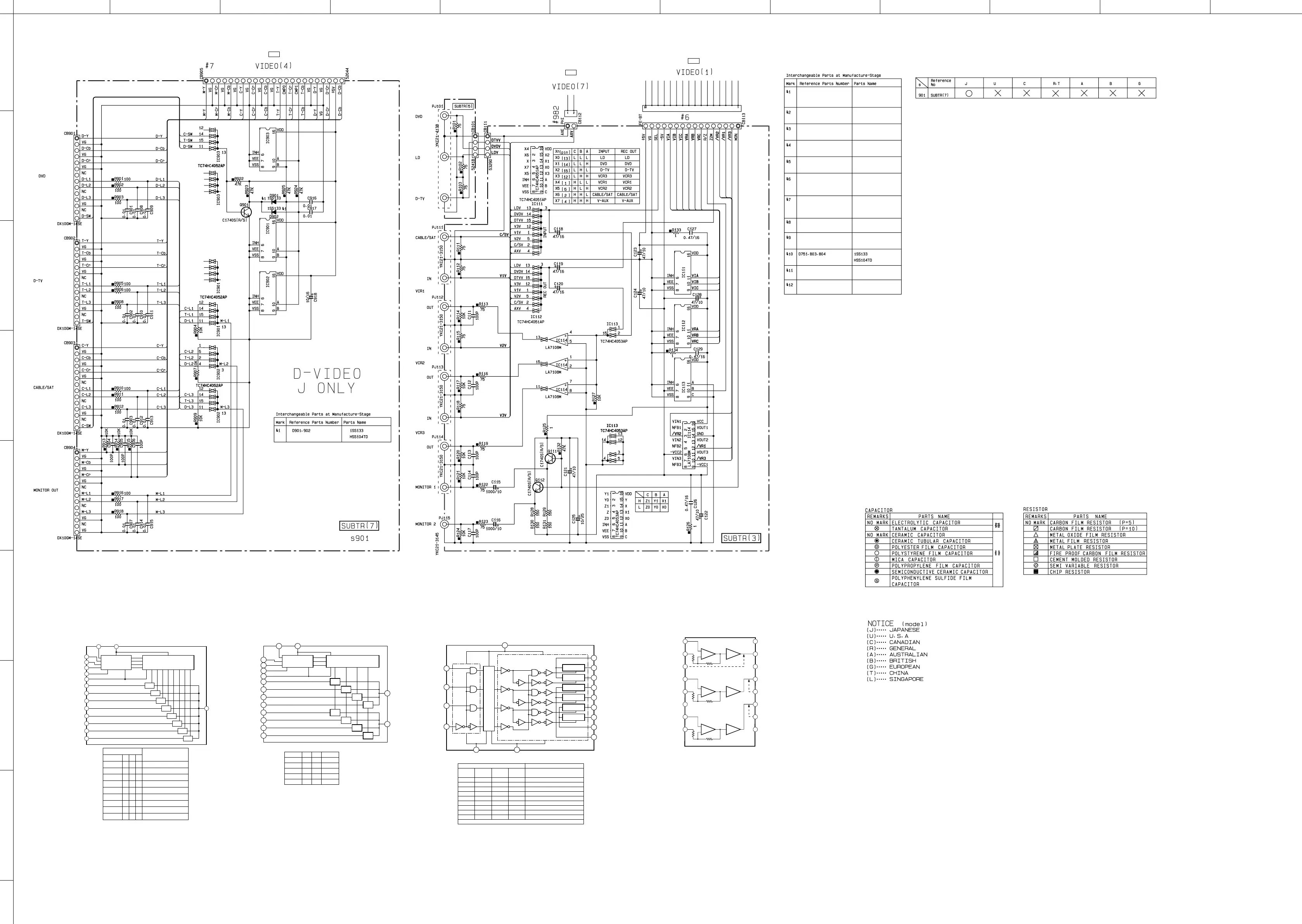

CIRCUIT CHANGES BY MARKET.

X : NOT USED

O : USED

■ SCHEMATIC DIAGRAM (SUB TRANS)

* All voltage are measured with a 10MΩ/V DC electric volt meter.

* Components having special characteristics are marked Z and

must be replaced with parts having specifications equal to those

originally installed.

* Schematic diagram is subject to change without notice.

LEVEL

CONVERTER

BINARY TO 1-OF-8

DECODER WITH INHIBIT

11

10

9

8

7

6 16

13

SW

SW

SW

SW

SW

SW

SW

SW

14

15

12

1

5

2

4

3

INHIBIT VDD

X

A

B

C

VSS

VEE

X0

X1

X2

X3

X4

X5

X6

X7

IC111, 112 : TC74HC4051AP

Analog Multiplexer/Demultiplexer

INPUT STATES

INHIBIT

0

0

0

0

0

0

0

0

1

C

0

0

0

0

1

1

1

1

X

B

0

0

1

1

0

0

1

1

X

A

0

1

0

1

0

1

0

1

X

“ON” CHANNEL (S)

0

1

2

3

4

5

6

7

NONE

IC113 : TC74HC4053AP

Triple 2-Channel Multiplexer/Demultiplexer

16

VDD

LOGIC LEVEL CONVERTER

12

OX

7

VEE

6

INH

OUT C IN

13

IX

OUT C IN

2

OY

OUT C IN

1

IY

OUT C IN

5

OZ

OUT C IN

3

IZ

OUT C IN

4

Z-COMMON

15

14

X-COMMON

Y-COMMON

9

C

10

B

11

A

8

VSS

INHIBIT

(Pin 6)

L

L

L

L

L

L

L

L

H

CONTROL INPUTS “ON” CHANNEL

0X (Pin 12), 0Y (Pin 2), 0Z (Pin 5)

1X (Pin 13), 1Y (Pin 1), 1Z (Pin 3)

0X, 0Y, 0Z

1X, 0Y, 0Z

0X, 1Y, 0Z

1X, 1Y, 0Z

0X, 0Y, 1Z

1X, 0Y, 1Z

0X, 1Y, 1Z

1X, 1Y, 1Z

NOTE

C

(Pin 9)

L

L

L

L

H

H

H

H

*

B

(Pin 10)

L

L

H

H

L

L

H

H

*

A

(Pin 11)

L

H

L

H

L

H

L

H

*

* Don’t Care

IC114 : LA7108M

75Ω Video Driver

6dB DR

6dB DR

6dB DR

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

VIN1+

NFB1

MUTE1

VIN2+

NFB2

–VCC1

VIN3+

NFB3

+VCC

VOUT1

GND

VOUT2

MUTE2

VOUT3

MUTE3

–VCC2

IC901~903 : TC74HC4052AP

Analog Multiplexers/Demultiplexers

16

VDD

6

INHIBIT

10

A

9

B

8

VSS

7

VEE

12

X0

14

X1

15

X2

11

X3

1

Y0

5

Y1

2

Y2

4

Y3

LEVEL

CONVERTER

BINARY TO 1-OF-4

DECODER WITH INHIBIT

SW

SW

SW

SW

SW

SW

SW

SW

13

X

3

Y

INHIBIT

0

0

0

0

1

B

0

0

1

1

X

A

0

1

0

1

X

0x, 0y

1x, 1y

2x, 2y

3x, 3y

NONE

E-99/J-91

P-E96/J88

E-1

P-E97/J89

F-2

P-E95/J87

E-1

Loading...

Loading...