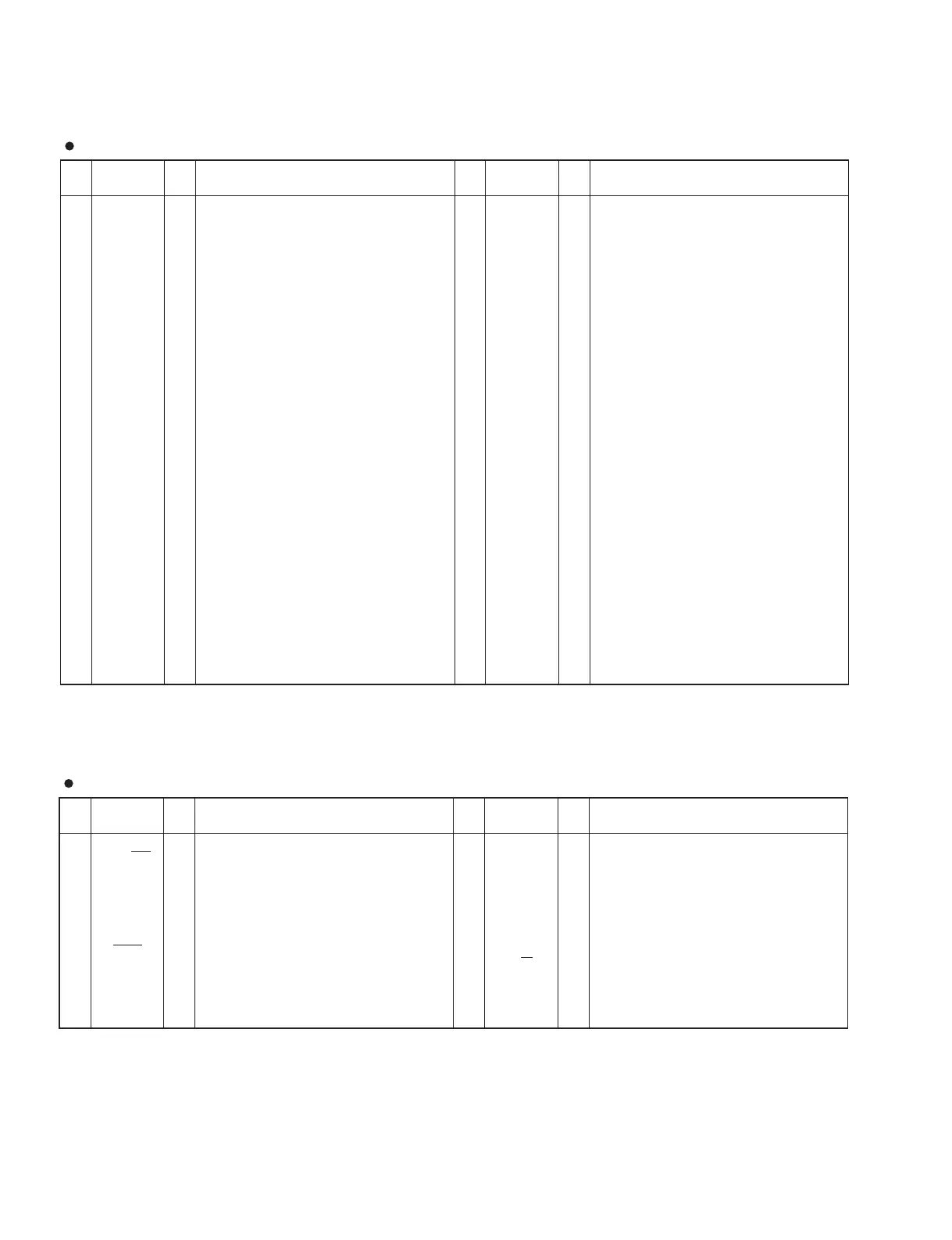

QL5/QL1

70

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

HD6433683E29FPV<(CPU()'&

QL5 FD1,FD2: IC002,IC202

QL1 FD1: IC002,IC202

$1

$1

$9

&&

;

;

9

&/

5(6

7(67

9

66

26&

26&

9

&&

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

,

,

,

2

,

,

,

,

,

2

,

,

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

$QDORJLQSXWSLQ

$QDORJLQSXWSLQ

$QDORJSRZHUVXSSO\SLQIRUWKH$'FRQYHUWHU

7KHVHSLQVFRQQHFWZLWKDN+]

FU\VWDOUHVRQDWRUIRUWKHVXEFORFN

7KHVHSLQVFRQQHFWZLWKDN+]

FU\VWDOUHVRQDWRUIRUWKHVXEFORFN

,QWHUQDOVWHSGRZQSRZHUVXSSO\SLQ

5HVHWSLQ

7HVWSLQ

*URXQGSLQ

7KHVHSLQVFRQQHFWZLWKFU\VWDORUFHUDPLFUHVRQDWRUIRU

WKHV\VWHPFORFNRUFDQEHXVHGWRLQSXWDQH[WHUQDOFORFN

7KHVHSLQVFRQQHFWZLWKFU\VWDORUFHUDPLFUHVRQDWRUIRU

WKHV\VWHPFORFNRUFDQEHXVHGWRLQSXWDQH[WHUQDOFORFN

3RZHUVXSSO\SLQ

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

3

3

10,

3

3

3

3

3

3

3

3

3

35;'

37;'

3

6&.B

5;'B

7;'B

3

3

3

3

3

3

3

3

3%$1

3%$1

3%$1

3%$1

3%$1

3%$1

,2

,2

,

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,2

,

2

,2

,2

,2

,2

,2

,2

,2

,2

,

,

,

,

,

,

ELW,2SRUW

ELW,2SRUW

1RQPDVNDEOHLQWHUUXSWUHTXHVWLQSXWSLQ

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW5HFHLYHGDWDLQSXWSLQ

ELW,2SRUW7UDQVPLWGDWDRXWSXWSLQ

ELW,2SRUW

&ORFN,2SLQ

5HFHLYHGDWDLQSXWSLQ

7UDQVPLWGDWDRXWSXWSLQ

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELW,2SRUW

ELWLQSXWSRUW$QDORJLQSXWSLQ

ELWLQSXWSRUW$QDORJLQSXWSLQ

ELWLQSXWSRUW$QDORJLQSXWSLQ

ELWLQSXWSRUW$QDORJLQSXWSLQ

ELWLQSXWSRUW$QDORJLQSXWSLQ

ELWLQSXWSRUW$QDORJLQSXWSLQ

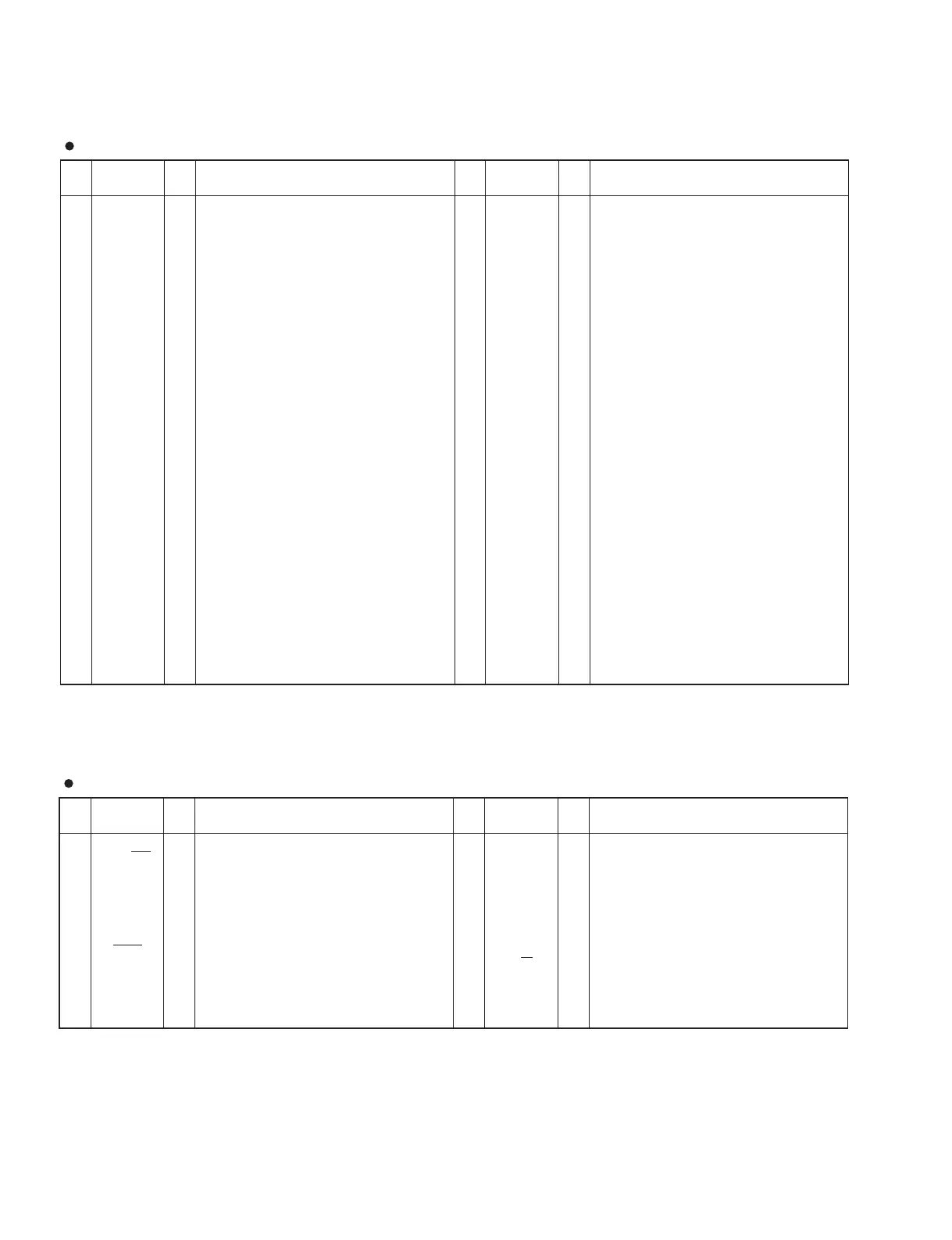

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

CS8406-CZZR (X8556A00) TRANSMITTER

JK: IC101

1

2

3

4

5

6

7

8

9

10

11

12

13

14

SDA/CDOUT

AD0/CS

AD2

RXP

TSTN

VD

TEST

TEST

RST

TEST

TEST

ILRCK

ISCLK

SDIN

I/O

I

I

I

I

I

I

I/O

I/O

I

Serial Control Data I/O (I²C Mode) / Data Out (SPI)

Address Bit 0 (I²C Mode) / Control Port Chip Select (SPI)

Address Bit 2 (I²C Mode)

Auxiliary AES3 Receiver Port

Test In

Digital Power

Test Pins

Test Pins

Reset

Test Pins

Test Pins

Serial Audio Input Left/Right Clock

Serial Audio Bit Clock

Serial Audio Data Port

15

16

17

18

19

20

21

22

23

24

25

26

27

28

TCBL

TEST

TEST

TEST

INT

U

OMCK

GND

VL

H/S

TXN

TXP

AD1/CDIN

SCL/CCLK

I/O

O

I

I

I

I

I

O

O

I

I

Transmit Channel Status Block Start

Test Pins

Test Pins

Test Pins

Interrupt

User Data

Master Clock

Ground

Logic Power

Hardware/Software Control Mode Select

Differential Line Drivers

Differential Line Drivers

Address Bit 1 (I²C Mode) / Serial Control Data in (SPI)

Control Port Clock

Loading...

Loading...