RFSoC Data Converter Evaluation Tool User Guide 18

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 3: Hardware Design

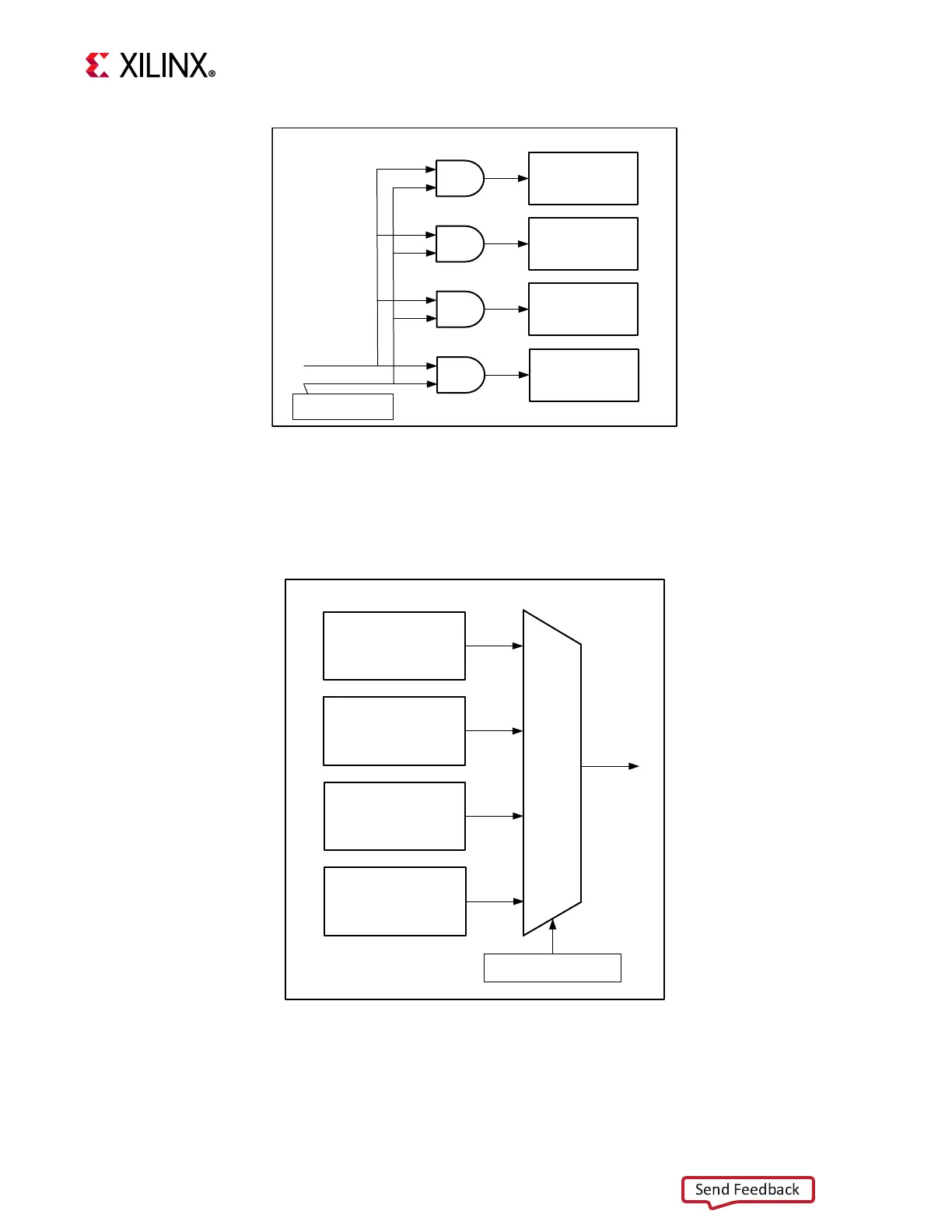

Figure 3-5 shows the TREADY signal generation. Only a single TREADY signal is selected

based on the Channel Select signal; other TREADY signals are ignored.

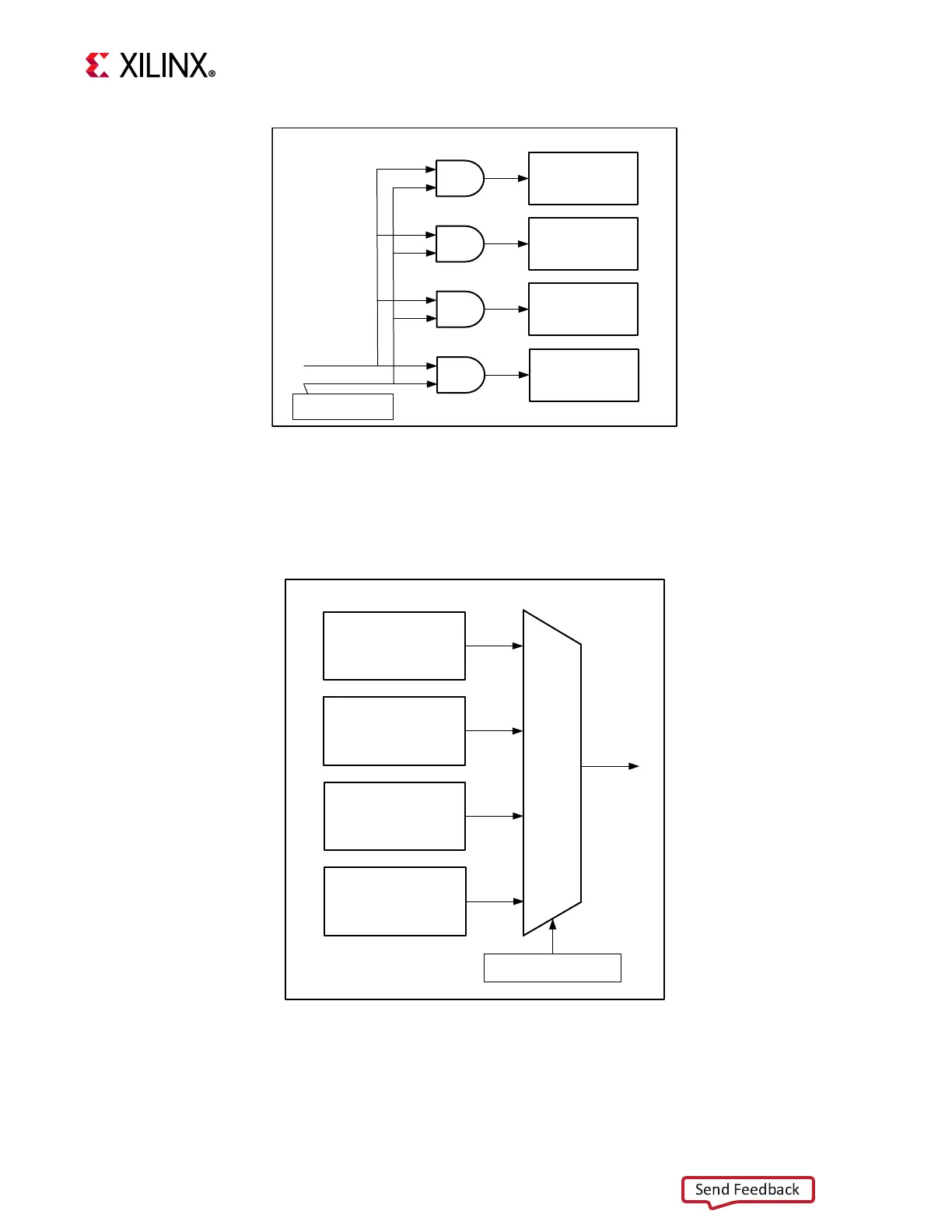

X-Ref Target - Figure 3-4

Figure 3-4: Channel Selection Control Signals

Tvalid 0..7

Memory

Loopback

0

Memory

Loopback

1

------------

Memory

Loopback

7

Channel Select 0..7

Channel Arbiter

X21236-092118

X-Ref Target - Figure 3-5

Figure 3-5: TREADY Signal Generation

Memory Loopback

0

Memory Loopback

1

------------

Memory Loopback

7

Mux

TReady

Channel Arbiter

X21237-092118

Loading...

Loading...