RFSoC Data Converter Evaluation Tool User Guide 29

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 4: Clocking

this signal is overridden with a global start/stop signal which is generated using Channel

Select of the Master DAC block, i.e., tile 0 block 0. This signal selection is controlled using

multi-tile mode select.

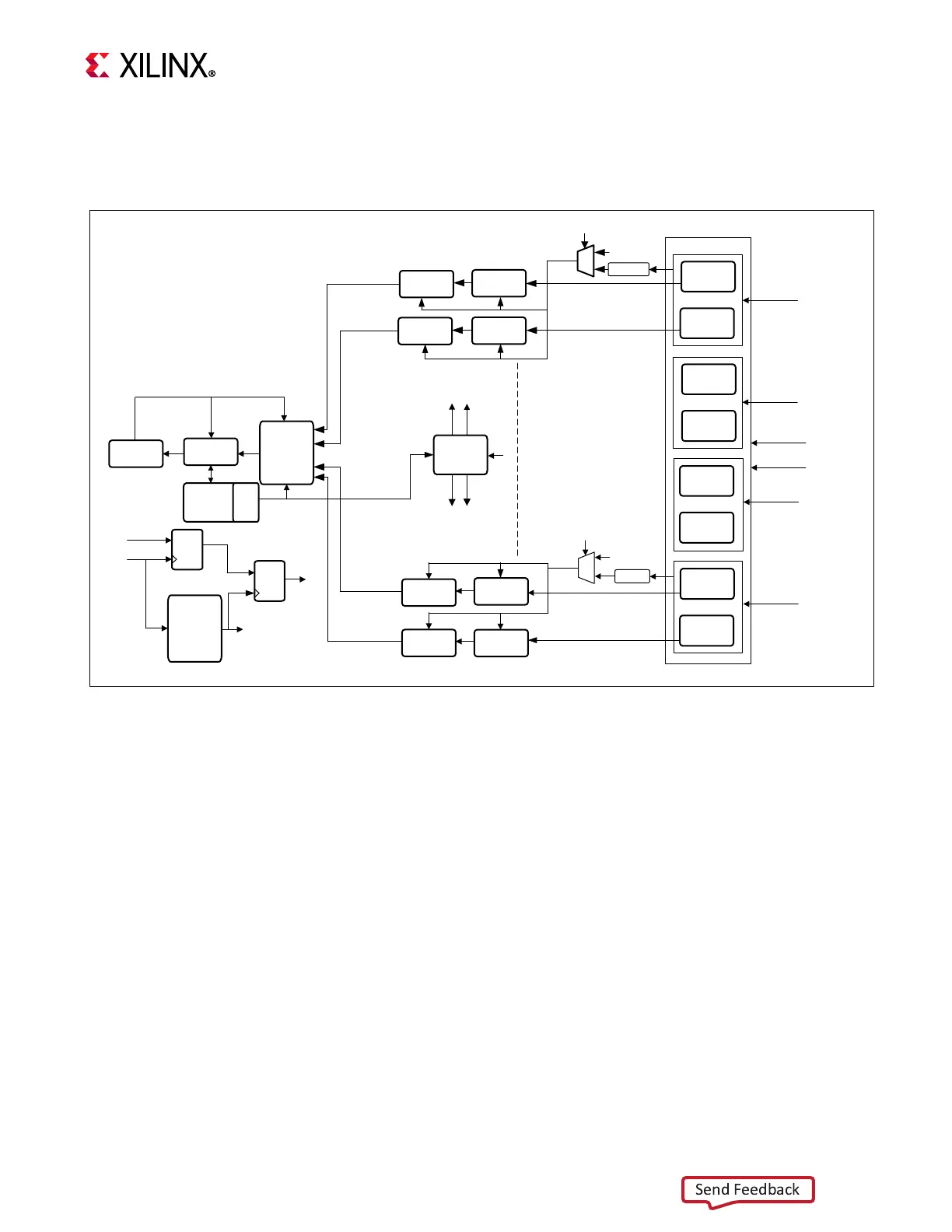

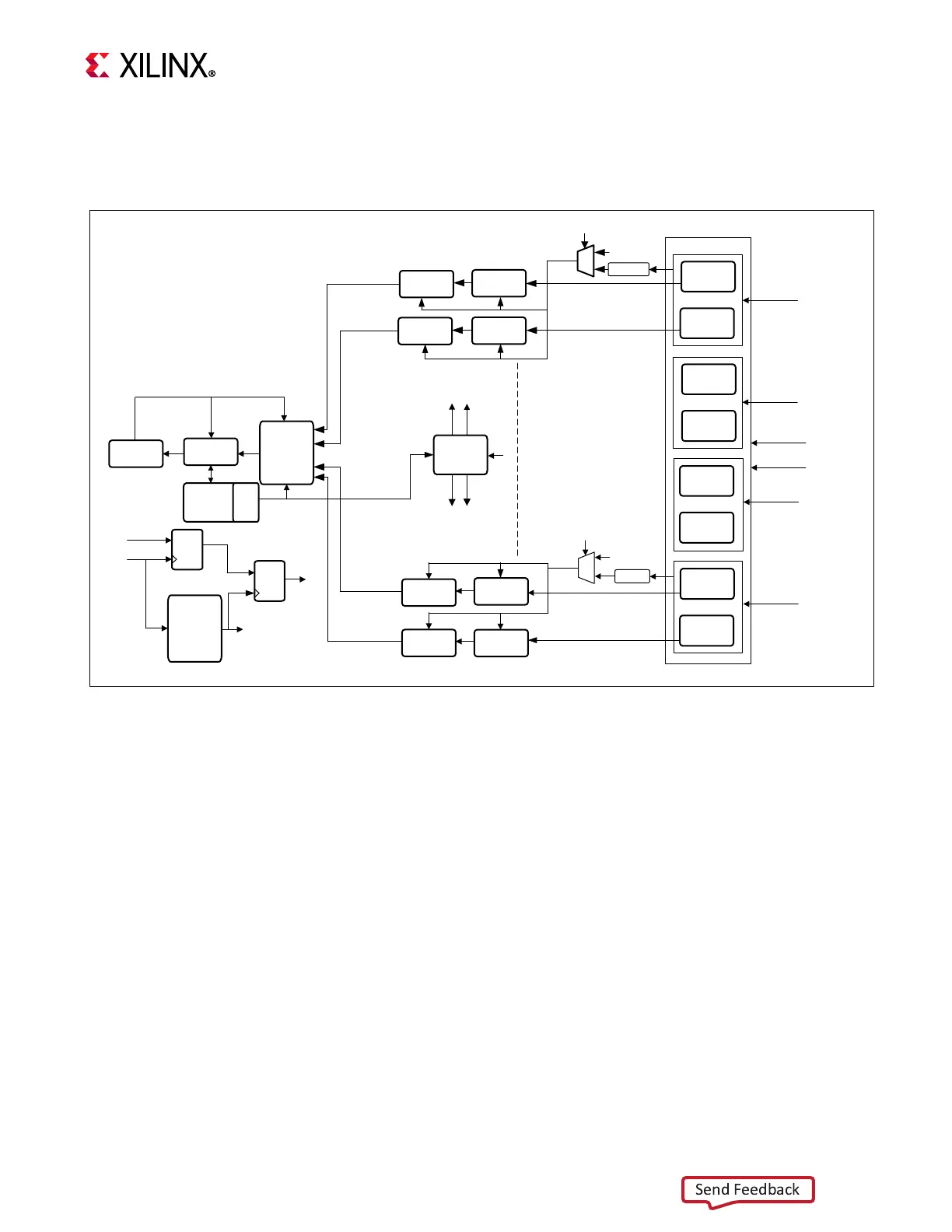

X-Ref Target - Figure 4-4

Figure 4-4: RF-ADC Multi-Tile Sync Clocking Structure

ADC 2

ADC 3

PL DDR +

MIG

DMA

Stream

Mux

ADC 4

ADC 5

ADC 6

ADC 7

333 MHz

ADC 0 Analog Clock (PCB)

ADC 1 Analog Clock (PCB)

SYSREF (PCB)

PL SYSREF (PCB)

PL REF CLK (PCB)

MMCM

PL CLK

(Fabric Clock)

User_sysref_adc

User_sysref_dac (Fabric Clock)

PL CLK

Example:

Fs = 3.2 GHz

Decimation = x1

SYREF = 8 MHz

PL SYSREF = 8 MHz

PL REF CLK = 200 MHz

Tile0 _ADC_Clock out

Tile 0

Tile 3

PS

GP

IO

Sync logic

To Tile1

channels

Multi-Tile Control

PL CLK = 400 MHz

AXIS FIFO

64 KS

AXIS FIFO

64 KS

I & Q

Merge

I & Q

Merge

AXIS FIFO

64 KS

I & Q

Merge

AXIS FIFO

64 KS

I & Q

Merge

To Tile3

channels

ADC 0

ADC 1

To Tile0

channels

To Tile2

channels

Tile 1

Tile 2

ADC 2 Analog Clock (PCB)

ADC 3 Analog Clock (PCB)

Tile0_clk

PL CLK

Tile3 _ADC_Clock out

Multi-Tile Control

Tile3_clk

PL

CLK

PLL

X21247-092118

PLL

Loading...

Loading...