RFSoC Data Converter Evaluation Tool User Guide 30

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 4: Clocking

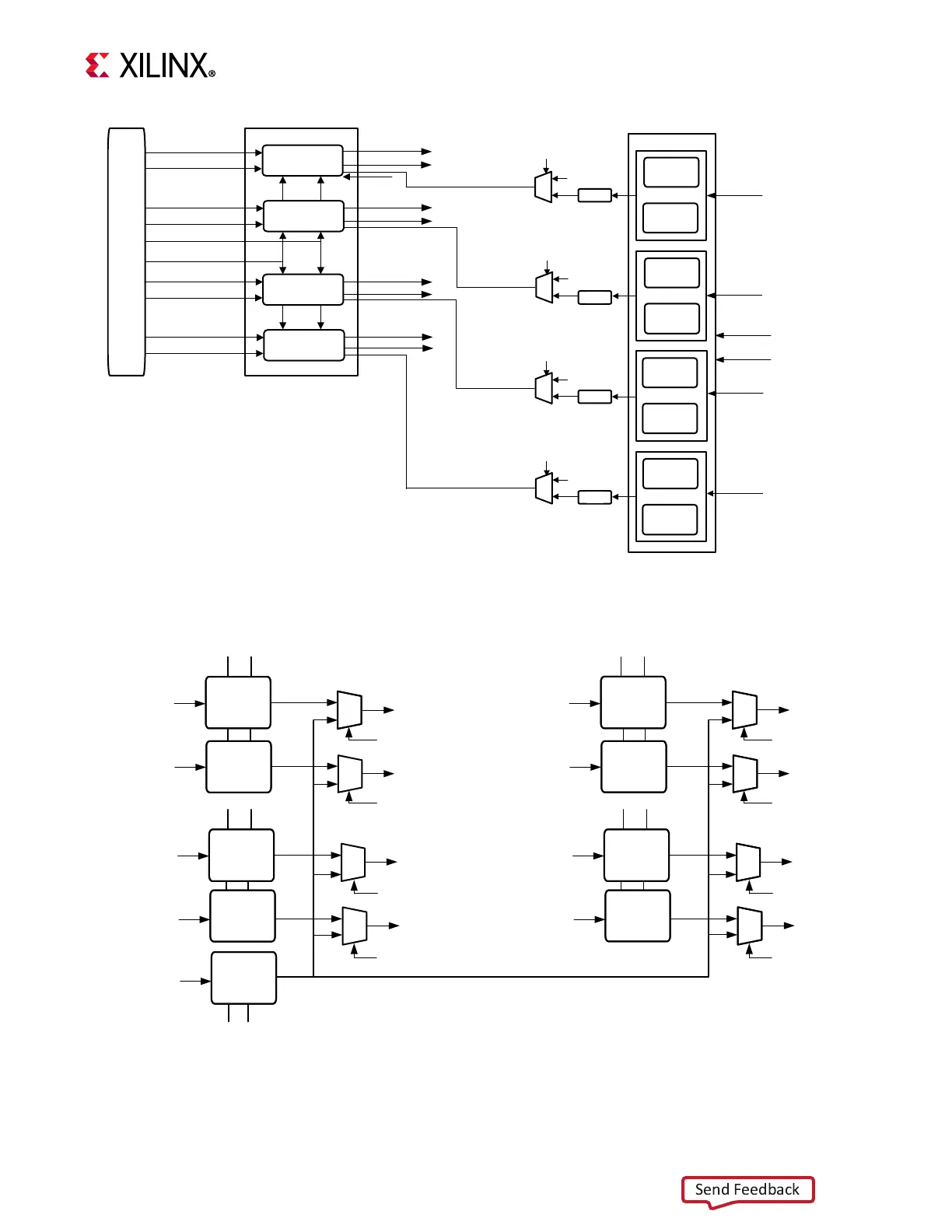

X-Ref Target - Figure 4-5

Figure 4-5: RF-ADC Control Signals for Multi-Tile Sync (Sync Block)

ADC 2

ADC 3

ADC 4

ADC 5

ADC 6

ADC 7

ADC 0 Analog Clock (PCB)

ADC 1 Analog Clock (PCB)

SYSREF (PCB)

User_sysref_dac (Fabric Clock)

PL CLK

Tile0 _ADC_Clock out

Tile 0

Tile 3

Multi-Tile Control

ADC 0

ADC 1

Tile 1

Tile 2

ADC 2 Analog Clock (PCB)

ADC 3 Analog Clock (PCB)

Tile0_clk

PL CLK

Tile3 _ADC_Clock out

Multi-Tile Control

Tile3_clk

PL CLK

Tile1 _ADC_Clock out

Multi-Tile Control

Tile1_clk

PL CLK

Tile2 _ADC_Clock out

Multi-Tile Control

Tile2_clk

N-stage

Sync logic

PS

GPIO

PS Clock

Multi-Tile Control

Channel 0 Control

Channel 1 Control

N-stage

Sync logic

Channel 2 Control

Channel 3 Control

N-stage

Sync logic

Channel 4 Control

Channel 5 Control

N-stage

Sync logic

Channel 6 Control

Channel 7 Control

ADC 0 Control

ADC 1 Control

ADC 2 Control

ADC 3 Control

ADC 4 Control

ADC 5 Control

ADC 6 Control

ADC 7 Control

PLL

PLL

PLL

PLL

PL CLK

X21248-092118

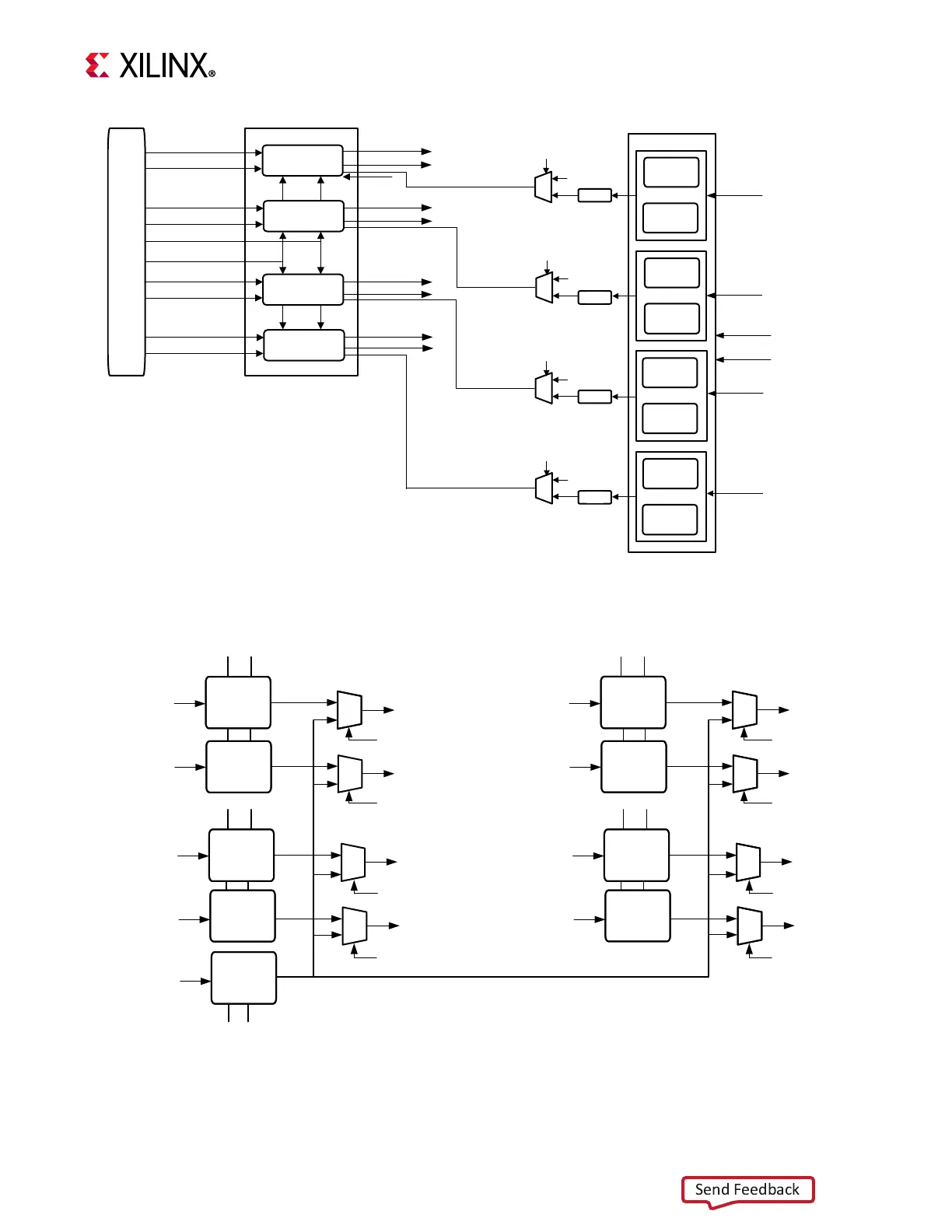

X-Ref Target - Figure 4-6

Figure 4-6: N-Stage Sync Logic for RF-ADC

Synchronizer

Channel 0 Control

Channel 1 Control

Channel 2 Control

Channel 3 Control

Synchronizer

Synchronizer

Synchronizer

Channel 0 Control

Synchronizer

Tile0 _clk

PS Clock

PLL CLK

PS Clock

Multi-Tile Control

ADC 0 CONTROL

Multi-Tile Control

ADC 1 CONTROL

Multi-Tile Control

ADC 2 CONTROL

Multi-Tile Control

ADC 3 CONTROL

Synchronizer

Channel 4 Control

Channel 5 Control

Channel 6 Control

Channel 7 Control

Synchronizer

Synchronizer

Synchronizer

Multi-Tile Control

ADC 4 CONTROL

Multi-Tile Control

ADC 5 CONTROL

Multi-Tile Control

ADC 6 CONTROL

Multi-Tile Control

ADC 7 CONTROL

Tile1 _clk

PS Clock

Tile2 _clk

PS Clock

Tile3 _clk

PS Clock

X21249-091318

Loading...

Loading...