RFSoC Data Converter Evaluation Tool User Guide 53

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 7: Protocol Specification

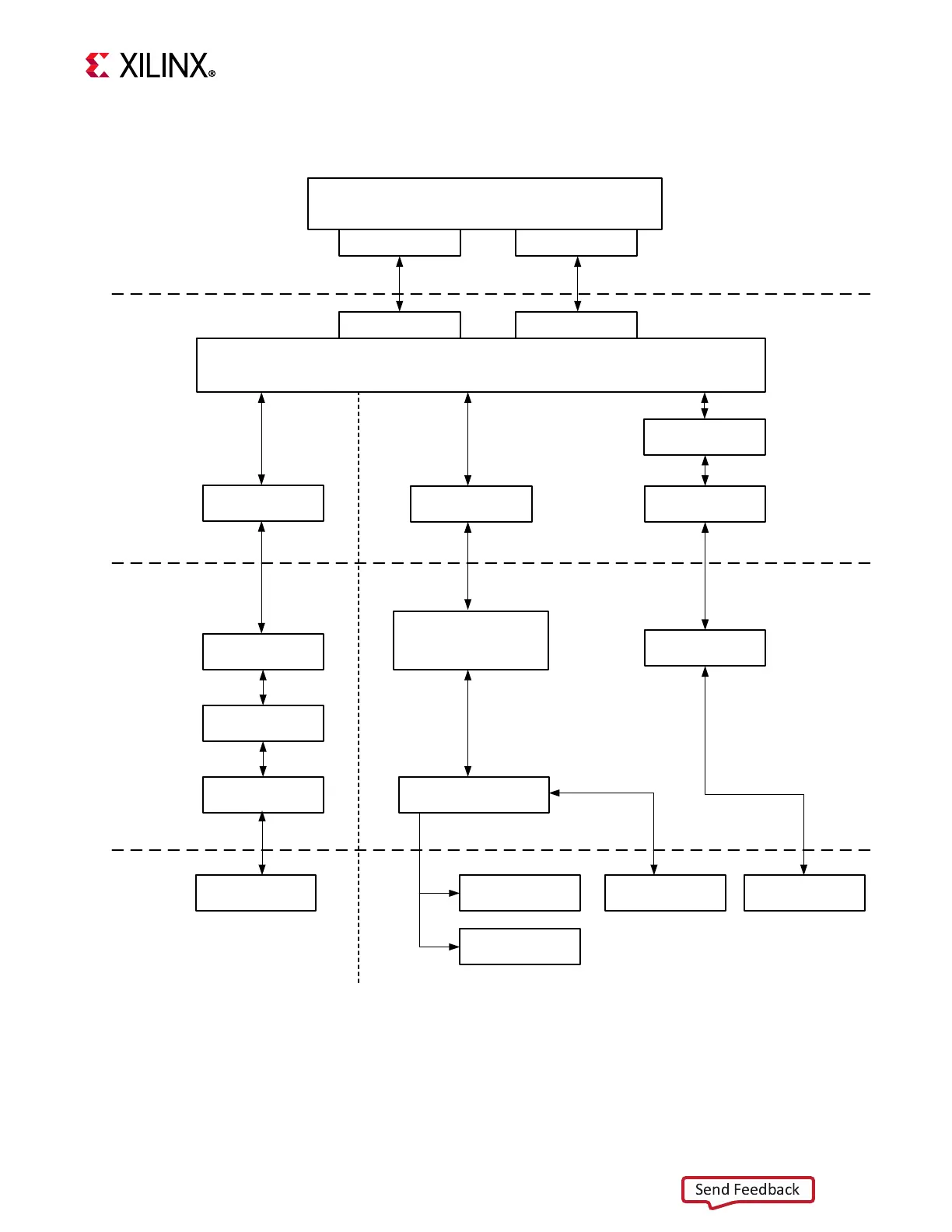

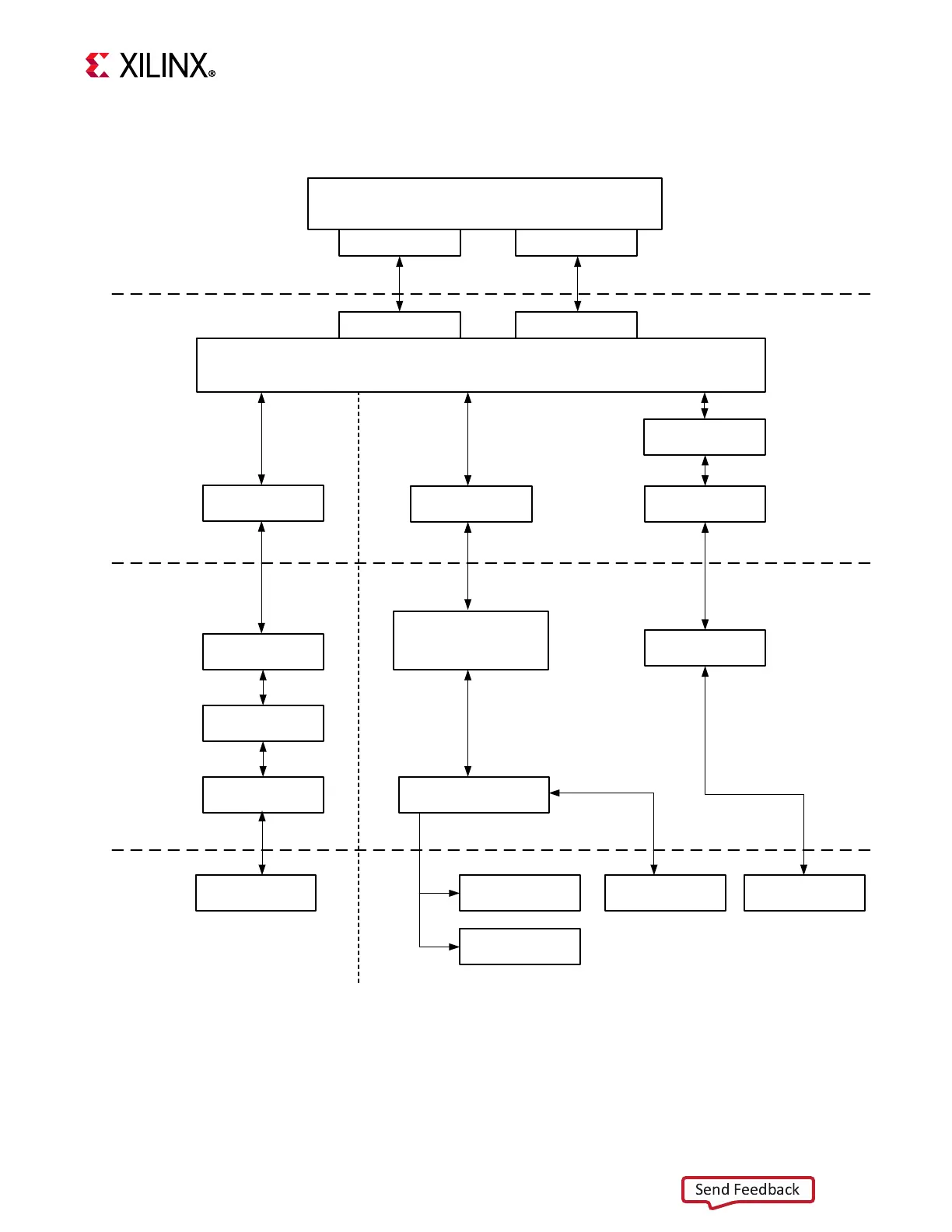

Figure 7-4 shows the control path and datapath flow.

X-Ref Target - Figure 7-4

Figure 7-4: Control and Datapath

Firmware/Application

TCP Socket

TCP Socket

sysfs

RFdc User Space

Driver

Libmetal

PL Memory Device

UIO

IIC Client Drivers

(Clock, Power, and Power

Measurement)

DMA Client Driver

AXI DMA Driver

DMA Engine

IIC Driver

AXI DMA Power Generator RFdc

TCP Socket

TCP Socket

Control Path

(TCP port 8081)

Datapath

(TCP port 8082)

Remote Machine

User Space

Kernel

Hardware

Power

Measurement

Clock Generator

Control Path

Datapath

*8,

X21258-091318

Loading...

Loading...