UG-1828 Preliminary Technical Data

Rev. PrC | Page 116 of 338

Delay Parameter Descriptions Bounds Notes

enableHoldDelay

(tRxEnaHold)

Delay between the hop

edge and disabling of the

Rx interface.

propagationDelay At the end of an Rx frame, or a sequence of

Rx frames, the interface can be left on,

even into the next frame, to allow for

propagation delay.

enableFallToOffDelay Delay between hop edge

and powering down the

LNA. Not used in frequency

hopping.

Min: 0

Max: 0

Hop edge indicates the end of frame on

air. The analog and Rx LNA can be

powered down immediately.

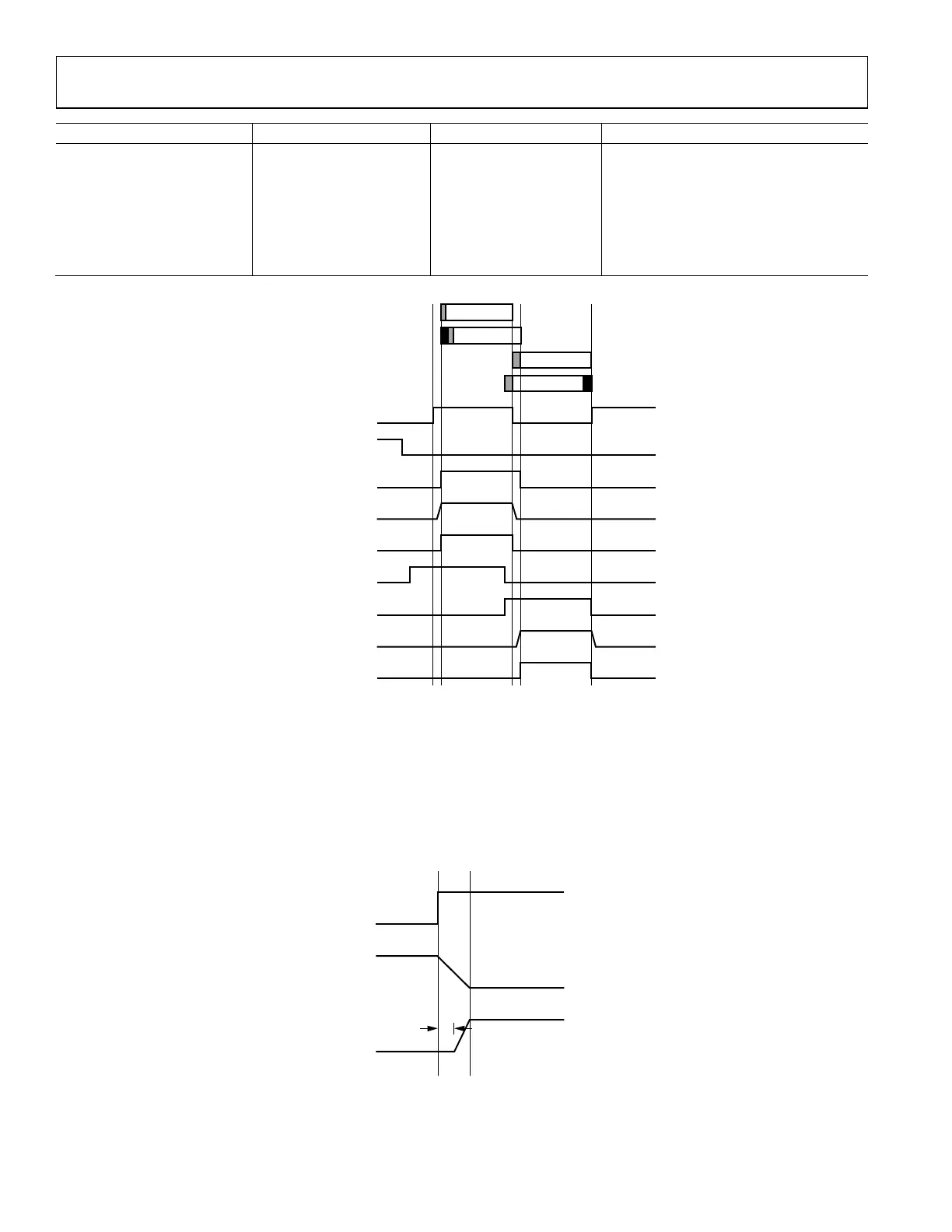

TRx Timing

Figure 116. TRx Timing

For TRx operation, because a hop edge can mark both the start and end of an Rx or Tx frame, the ADRV9001 guarantees that the Rx front

end and Tx front end are not powered up at the same time.

To achieve this, ADRV9001 enforces a minimum setting for RxRiseToAnaOn, specified by analogGuardTime, to ensure that the Rx front

end is powered up after the Tx front end is powered down.

No minimum setting for TxRiseToAnaOn is required. This is because the Rx front end is always powered down before the Tx front end

power up routine starts, and no extra delay is required.

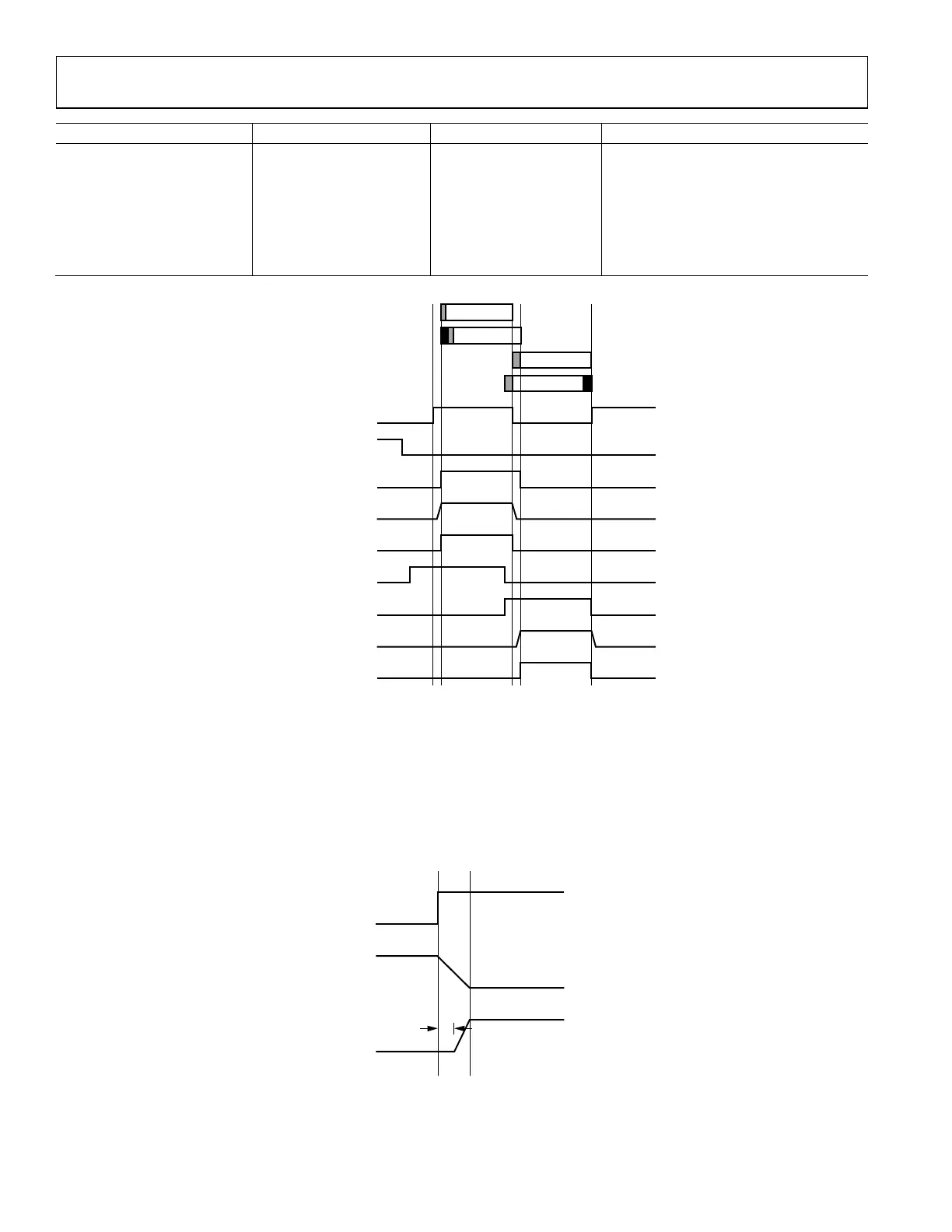

Figure 117. TxRiseToAnaOn

PLL Retune

In PLL retune mode, the time to the start of the Rx/Tx analog front end being powered up is the maximum of t

pllRetune

and t

chRiseToAnaOn

.

Rx

Tx

Tx

Rx

Tx ON: ANTENNA SWITCH

Rx ON: LNA POWER OUT

Rx FRAMING ON AIR

Rx FRAMING AT BBIC

Tx FRAMING ON AIR

Tx FRAMING AT BBIC

PIN: HOP

PIN: Rx SETUP

PIN: Tx SETUP

Tx INTERFACE

Rx INTERFACE

Tx ANALOG POWER

Rx ANALOG POWER

24159-492

HOP

Tx AFE

Rx AFE

t

RxRiseToAnaOn

24159-493

Loading...

Loading...