UG-1828 Preliminary Technical Data

Rev. PrC | Page 120 of 338

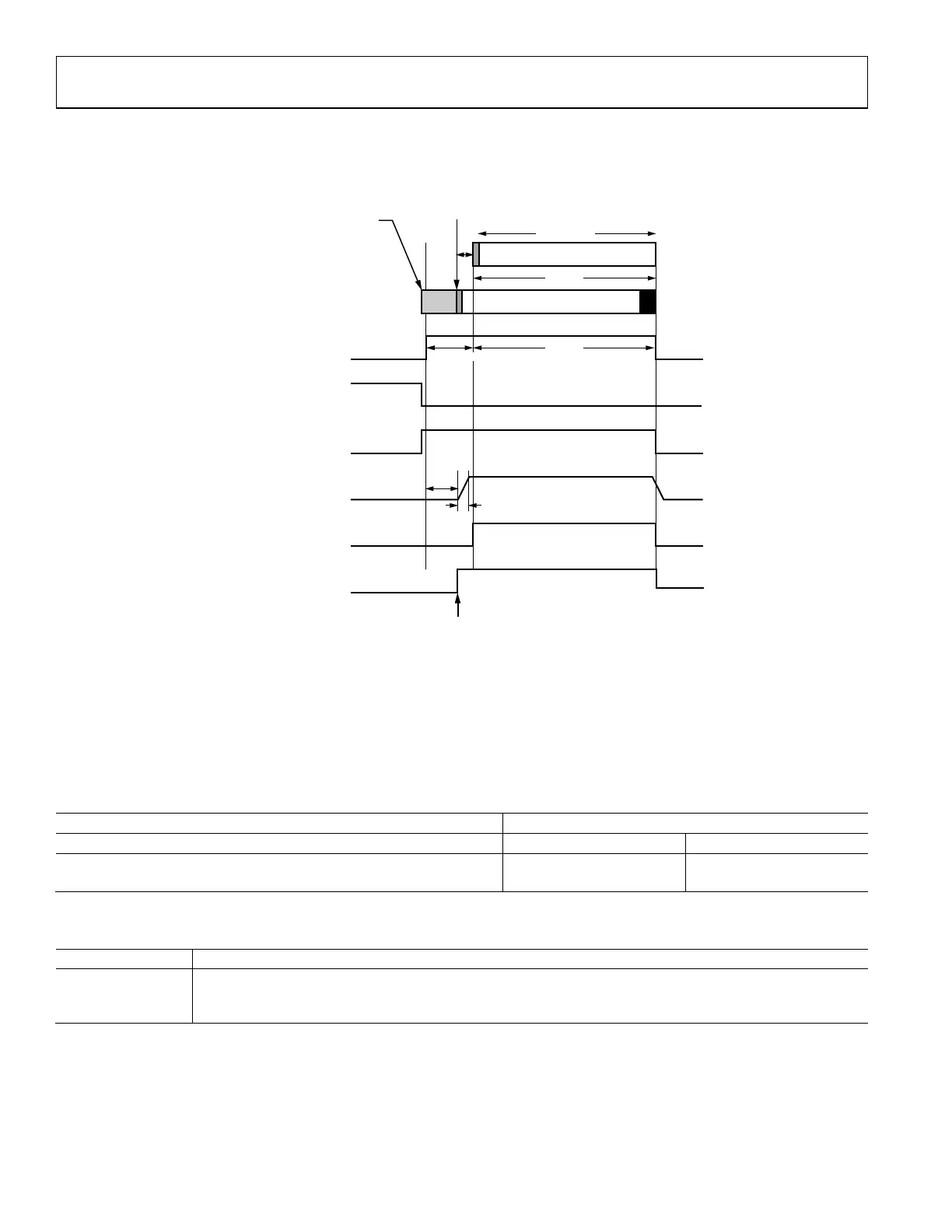

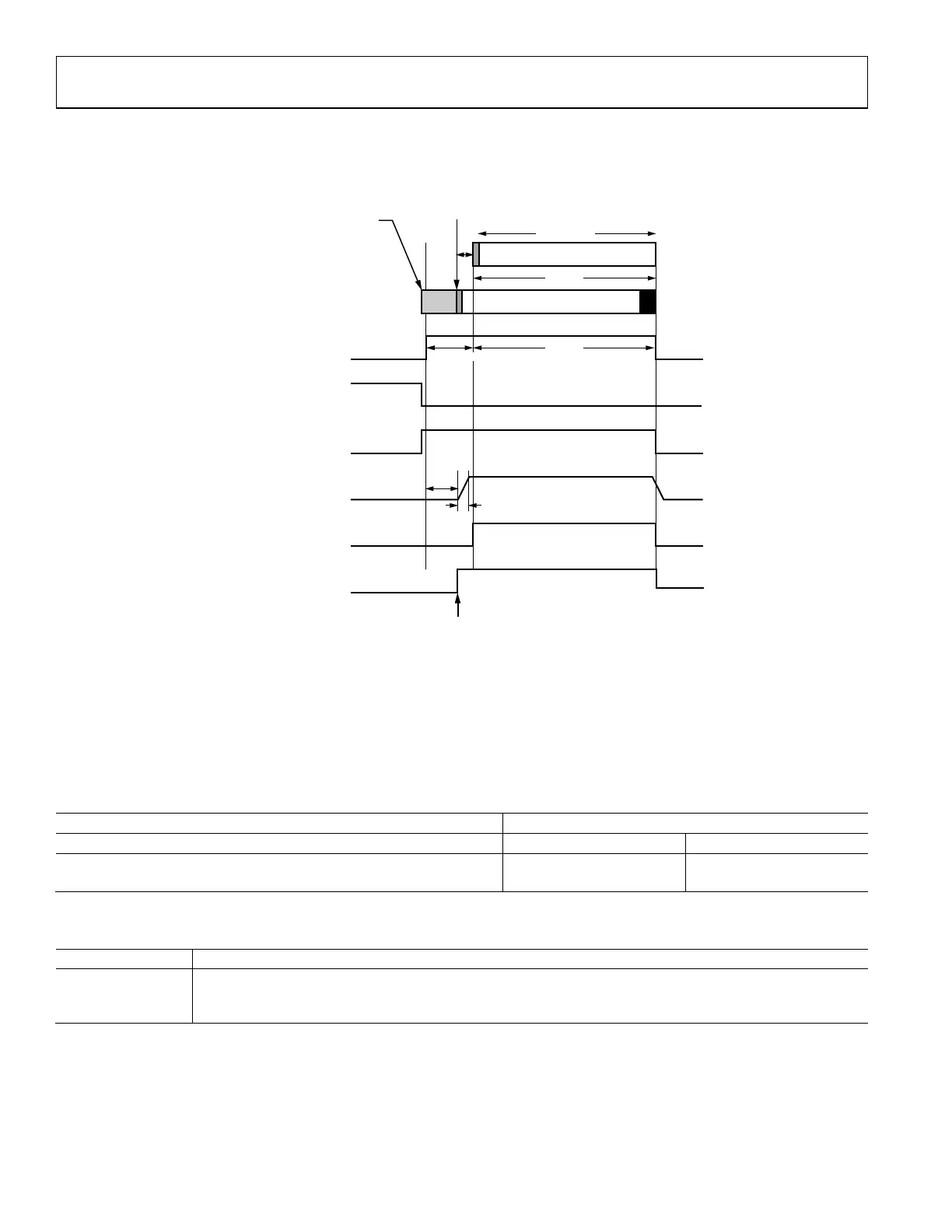

Figure 123, shows another althernative method, where user can hold off from their transmission until t

propagationDelay

prior to the analog front

end being enabled. Here the FPGA Tx DMA is involved to delay the transmitting data until analog front end is ready.

Figure 123. Tx Only with Short Propagation Delay, FPGA Delay

ORx Operation

ADRV9001 supports ORx operation in frequency hopping mode. ORx in frequency hopping works in the same way as normal TDD

mode. During the actual Tx frame, the user can set the ORx enable signal high to enable ORx.

The user must then set ORx low (disable ORx) before the end of the frame. This is required regardless of whether the next frame is Tx or Rx.

The user must take the ORx setup and bring-down time into consideration, as well as the propagation delay of their profile.

Table 44. ORx Timing Parameters Time Required

Timing Parameter Time Required (us)

tOrxRiseToOn 8 9

tOrxFallToOff 6 5

Table 45. ORx Timing Parameters Timing Restrictions

Timing Parameter Timing Restriction

tHopEdgeToORxRise Must be greater than the transition time, or tTxRiseToOn

tORxFallToHopEdge Enough time for the ORx disable to complete. At least TBD us, however it is recommended to add some guard

time to that (for example, 1 µs)

When using ORx in frequency hopping, the user must take into consideration the following parameters when determining their frame

duration:

• ORx enable rising edge time (t

OrxRiseToOn)

• ORx enable falling edge time (t

OrxFallToOff)

• Propagation delay (t

propagationDelay)

24159-498

FRAMING ON AIR

USER STARTS

SENDING FIXED

PATTERNS/ZEROS

USER STARTS

SENDING

VALID DATA

USER ENABLES

FPGA Tx DMA

FRAMING AT BBIC

PIN: HOP

PIN: Rx SETUP

Tx INTERFACE

Tx ANALOG POWER

Tx ON: ANTENNA SWITCH

FPGA Tx DMA

t

RxPD

t

TxEnaRise2AnaOn

t

TxEnaSetup

ZEROS/

PATTERN

VALID DATA

TRANSITION

DWELL

DWELL

NOT

ON

AIR

Loading...

Loading...