Bosch Sensortec"| BST-BMP581-DS004-02 51 | 74

Modifications reserved | Data subject to change

without notice Document number: BST-BMP581-DS004-02

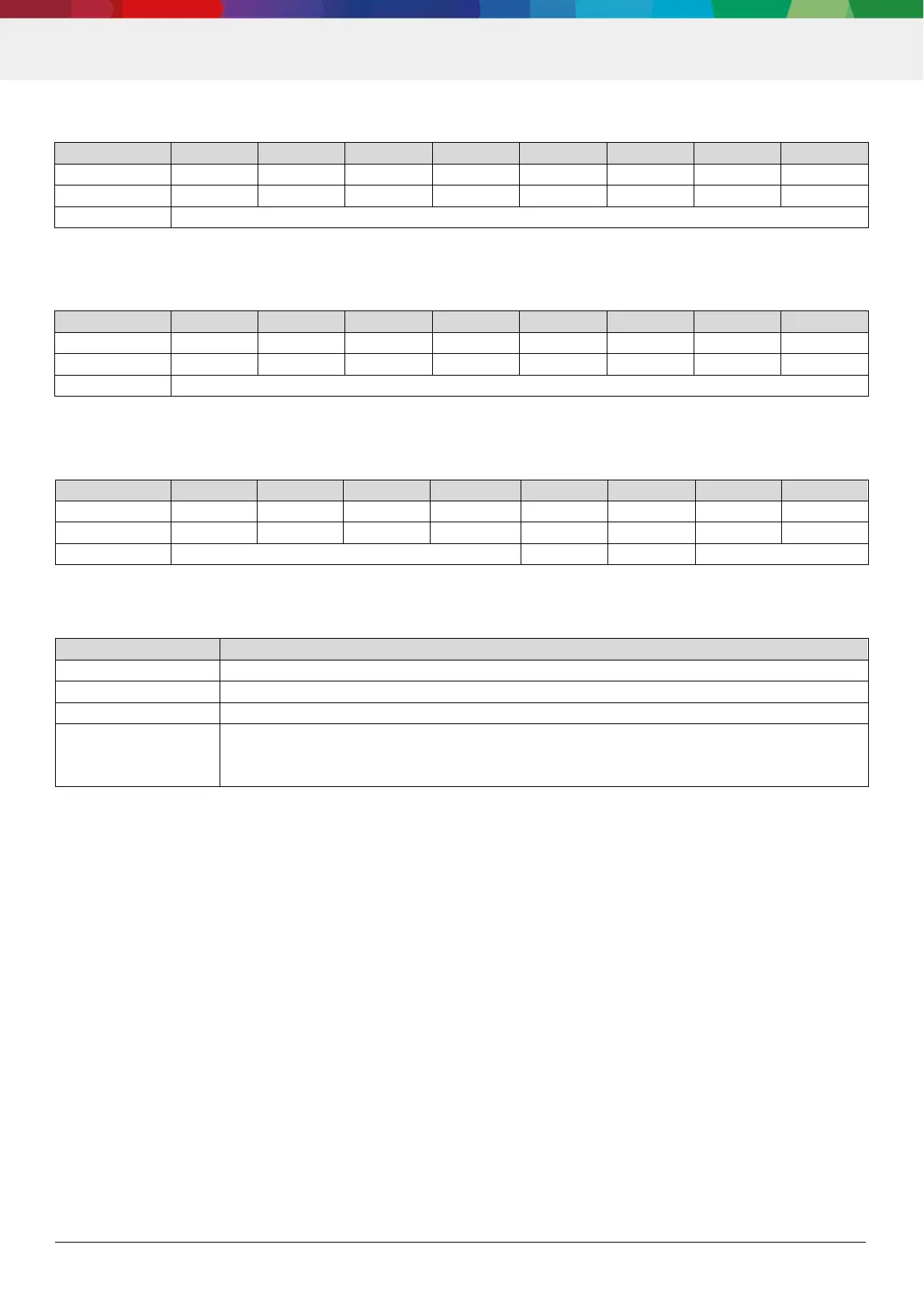

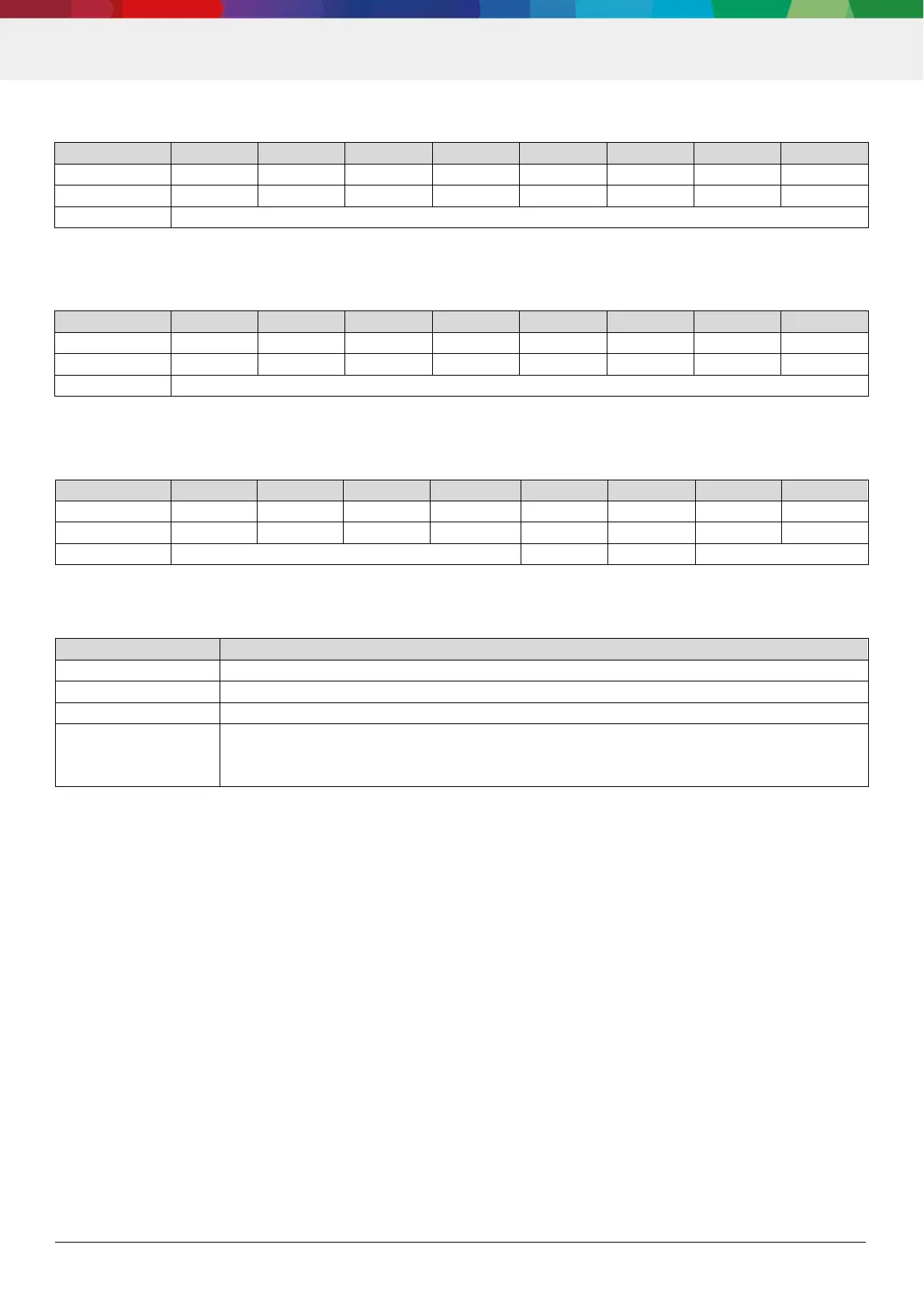

7.1 Register (0x01) ASIC identification ID

chip_id:(bit offset: 0) ASIC ID

7.2 Register (0x02) ASIC revision ID

asic_rev_id:(bit offset: 0) ASIC revision

7.3 Register (0x11) ASIC status register

hif_mode:(bit offset: 0) HIF mode (NVM-backed)

I2C Mode Only [SPI disabled]

SPI and I2C Available (Autoconfig) Interface selection is automatically configured. Default is

I2C mode. During Power-on CSB pin should be tied to VDDIO to pull it high at power-on. If

CSB goes low during, I2C interface will be disabled until the next power-on-reset.

i3c_err_0:(bit offset: 2) SDR parity error occurred

i3c_err_3:(bit offset: 3) S0/S1 error occurred. When S0/S1 error occurs, the slave will recover automatically after 60us

as if an HDR-exit pattern is executed on the bus. Flag will persist for notification purpose. This flag is clear-onread

type. It is cleared automatically once read.

reserved_7_4:(bit offset: 4) reserved

Loading...

Loading...