PRELIMINARY

Document type: Title: Revision date: Revision:

User's Manual (MUT) Mod. V1729 4 Channel 12 Bit Sampling ADC 22/06/2005 3

NPO: Filename: Number of pages: Page:

00109/04:V1729.MUTx/03 V1729_REV3.DOC 38 33

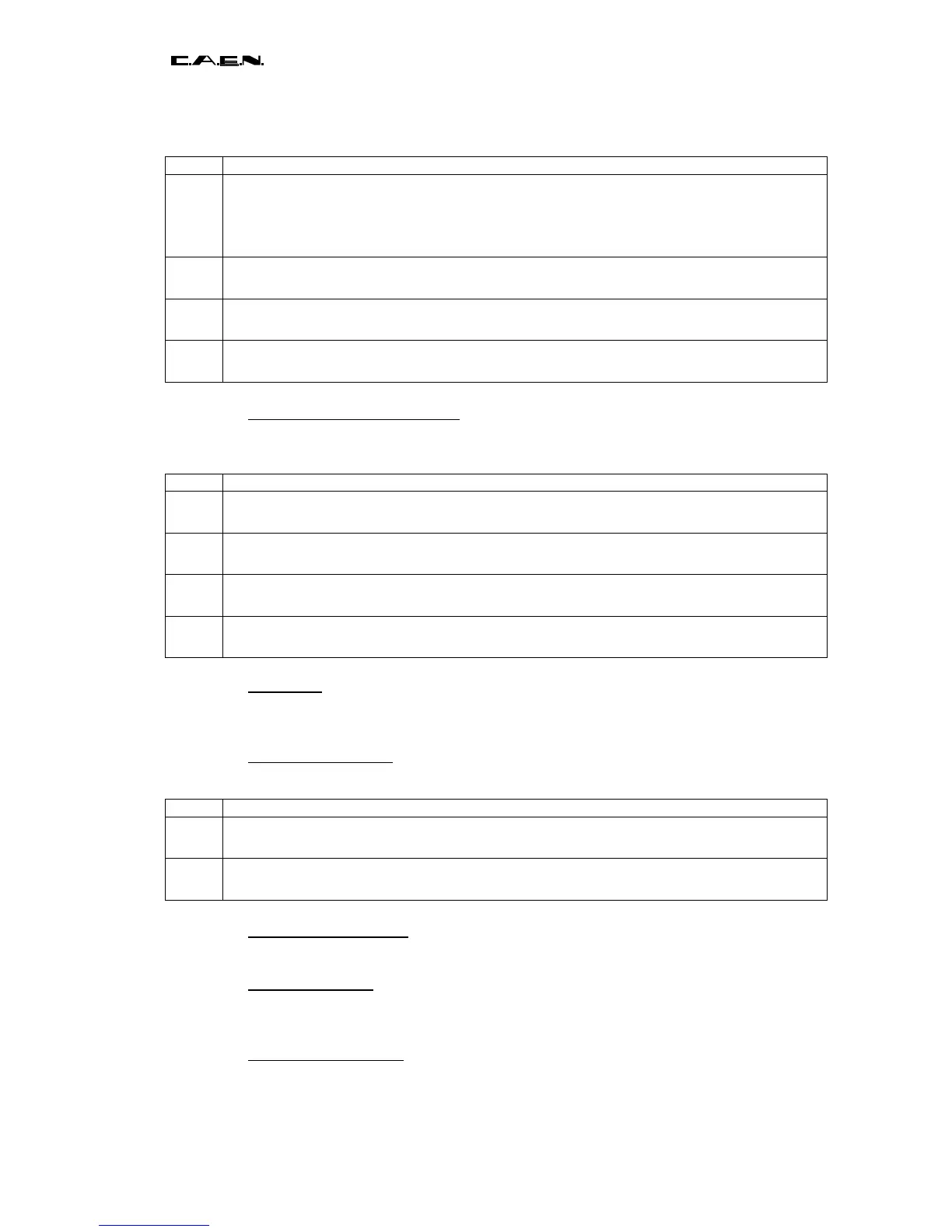

Bits Function

0-1

Val = 0 => SOFTWARE TRIGGER

Val = 1 => trigger on discriminator (threshold fixed by the DAC)

Val = 2 => external trigger from the TRIG_EXT input

Val = 3 => logic “OR” of SOFTWARE TRIGGER and trigger on discriminator

2

Val = 0 => rising edge

Val = 1 => falling edge

3

Val = 0 => Inhibites random internal trigger.

Val = 1 => Authorizes random internal trigger.

4

Val = 0 => one uses the Trigger normally.

Val = 1 => one uses the external Trigger directly and without masking.

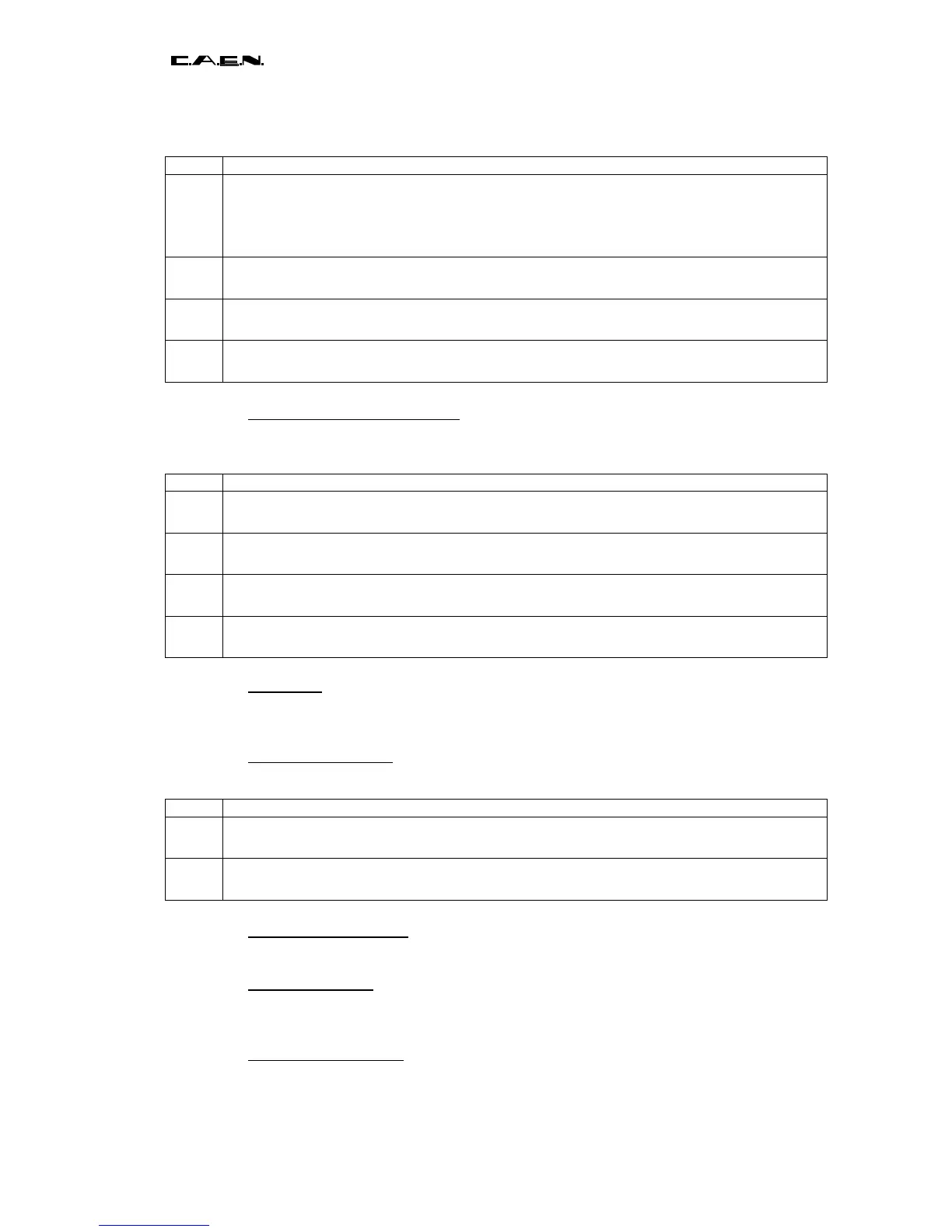

TRIGGER CHANNEL SOURCE : this 4-bit register fixes the channel(s) from which the

discriminators will release the trigger. More than one channel can be validated at the

same time because one realizes a logic « OR » of the outputs of the discriminators in the

controller.

Bits Function

0

Val = 0 => Disables Trigger on channel 0.

Val = 1 => Enables Trigger on channel 0.

1

Val = 0 => Disables Trigger on channel 1.

Val = 1 => Enables Trigger on channel 1.

2

Val = 0 => Disables Trigger on channel 2.

Val = 1 => Enables Trigger on channel 2.

3

Val = 0 => Disables Trigger on channel 3.

Val = 1 => Enables Trigger on channel 3.

TRIG_REC

: this 8-bit register gives the distance between the column where one finds

the column pointer at the arrival time of the synchronous trigger and the last column

(128). It permits in practice to roughly date the useful signal to the nearest clock rising

edge. This dating will be refined with greater precision by the utilization of the vernier.

FAST READ MODES

: this 2-bit register permits realization of a faster reading of the

MATACQ chips. Usage reserved for experts for it may have an influence on the noise

level.

Bits Function

0

Val = 0 => sequence with reading of TRIG_REC (normal)

Val = 1 => sequence without reading of TRIG_REC (fast)

1

Val = 0 => sequence departing from the first column (normal)

Val = 1 => sequence departing from the STOP (fast)

NB OF COLS TO READ : this 8-bit register gives the number of columns that one wants

to read in the matrix. The number of columns can be fixed between 0 et 128. The stored

value is by default 128, which corresponds to the whole matrix.

CHANNEL MASKS

: each one of the 4 bits in this register individually validates a channel

on the board. For this, they must be set at 1. At zero, the corresponding channel is

masked and its data will not be recorded in the RAM. Caution : this modifies the format of

the frame stored in the RAM (see IV.3).

POST STOP LATENCY

: this register permits the programming with steps of 2.5μs of the

time during which the board waits for the validation signal in the mode where the latter is

Loading...

Loading...