CY7C68013

Document #: 38-08012 Rev. *A Page 24 of 48

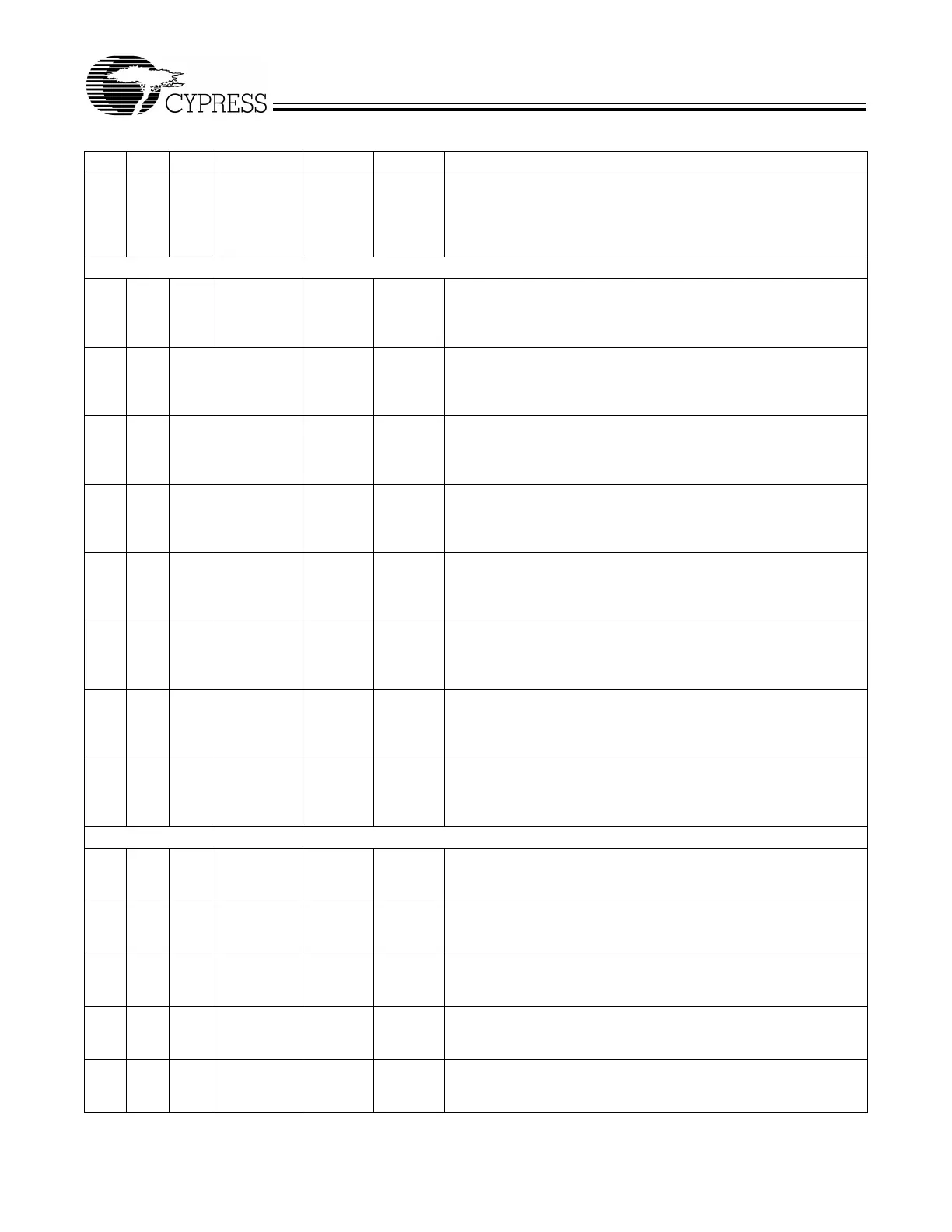

92 74 47 PA7 or

FLAGD or

SLCS#

I/O/Z I

(PA7)

Multiplexed pin whose function is selected by the IFCONFIG[1:0] and

PORTACFG.7 bits.

PA7 is a bidirectional I/O port pin.

FLAGD is a programmable slave-FIFO output status flag signal.

SLCS# gates all other slave FIFO enable/strobes

Port B

44 34 25 PB0 or

FD[0]

I/O/Z I

(PB0)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB0 is a bidirectional I/O port pin.

FD[0] is the bidirectional FIFO/GPIF data bus.

45 35 26 PB1 or

FD[1]

I/O/Z I

(PB1)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB1 is a bidirectional I/O port pin.

FD[1] is the bidirectional FIFO/GPIF data bus.

46 36 27 PB2 or

FD[2]

I/O/Z I

(PB2)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB2 is a bidirectional I/O port pin.

FD[2] is the bidirectional FIFO/GPIF data bus.

47 37 28 PB3 or

TXD1 or

FD[3]

I/O/Z I

(PB3)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB3 is a bidirectional I/O port pin.

FD[3] is the bidirectional FIFO/GPIF data bus.

54 44 29 PB4 or

FD[4]

I/O/Z I

(PB4)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB4 is a bidirectional I/O port pin.

FD[4] is the bidirectional FIFO/GPIF data bus.

55 45 30 PB5 or

FD[5]

I/O/Z I

(PB5)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB5 is a bidirectional I/O port pin.

FD[5] is the bidirectional FIFO/GPIF data bus.

56 46 31 PB6 or

FD[6]

I/O/Z I

(PB6)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB6 is a bidirectional I/O port pin.

FD[6] is the bidirectional FIFO/GPIF data bus.

57 47 32 PB7 or

FD[7]

I/O/Z I

(PB7)

Multiplexed pin whose function is selected by the following bits:

IFCONFIG[1..0].

PB7 is a bidirectional I/O port pin.

FD[7] is the bidirectional FIFO/GPIF data bus.

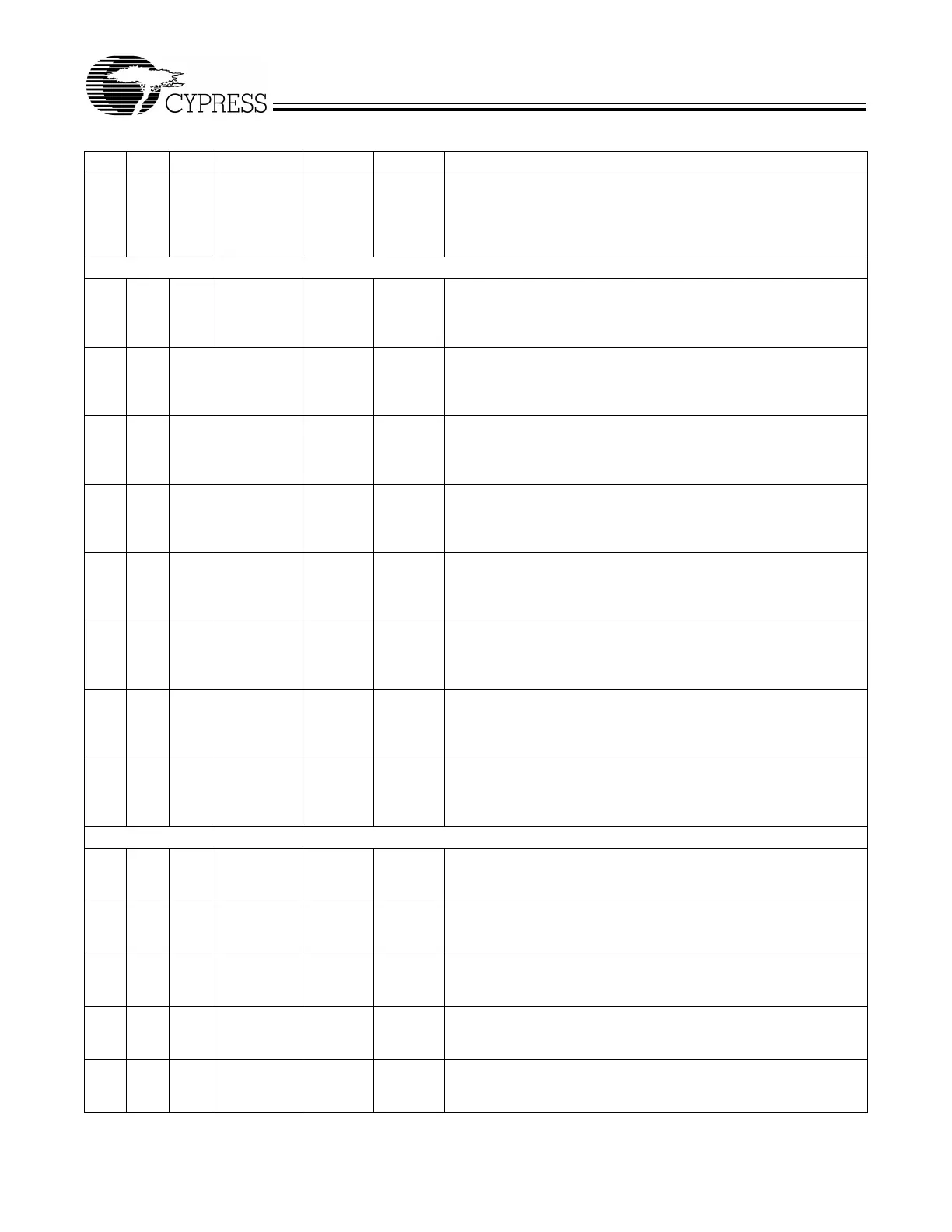

PORT C

72 57 PC0 or

GPIFADR0

I/O/Z I

(PC0)

Multiplexed pin whose function is selected by PORTCCFG.0

PC0 is a bidirectional I/O port pin.

GPIFADR0 is a GPIF address output pin.

73 58 PC1 or

GPIFADR1

I/O/Z I

(PC1)

Multiplexed pin whose function is selected by PORTCCFG.1

PC1 is a bidirectional I/O port pin.

GPIFADR1 is a GPIF address output pin.

74 59 PC2 or

GPIFADR2

I/O/Z I

(PC2)

Multiplexed pin whose function is selected by PORTCCFG.2

PC2 is a bidirectional I/O port pin.

GPIFADR2 is a GPIF address output pin.

75 60 PC3 or

GPIFADR3

I/O/Z I

(PC3)

Multiplexed pin whose function is selected by PORTCCFG.3

PC3 is a bidirectional I/O port pin.

GPIFADR3 is a GPIF address output pin.

76 61 PC4 or

GPIFADR4

I/O/Z I

(PC4)

Multiplexed pin whose function is selected by PORTCCFG.4

PC4 is a bidirectional I/O port pin.

GPIFADR4 is a GPIF address output pin.

Table 4-1. FX2 Pin Descriptions

[5]

(continued)

128 100 56 Name Type Default Description

Loading...

Loading...