Cypress EZ-USB CX3

EZ-USB® CX3 Technical Reference Manual, Doc. No. 001-91492 Rev. *B 17

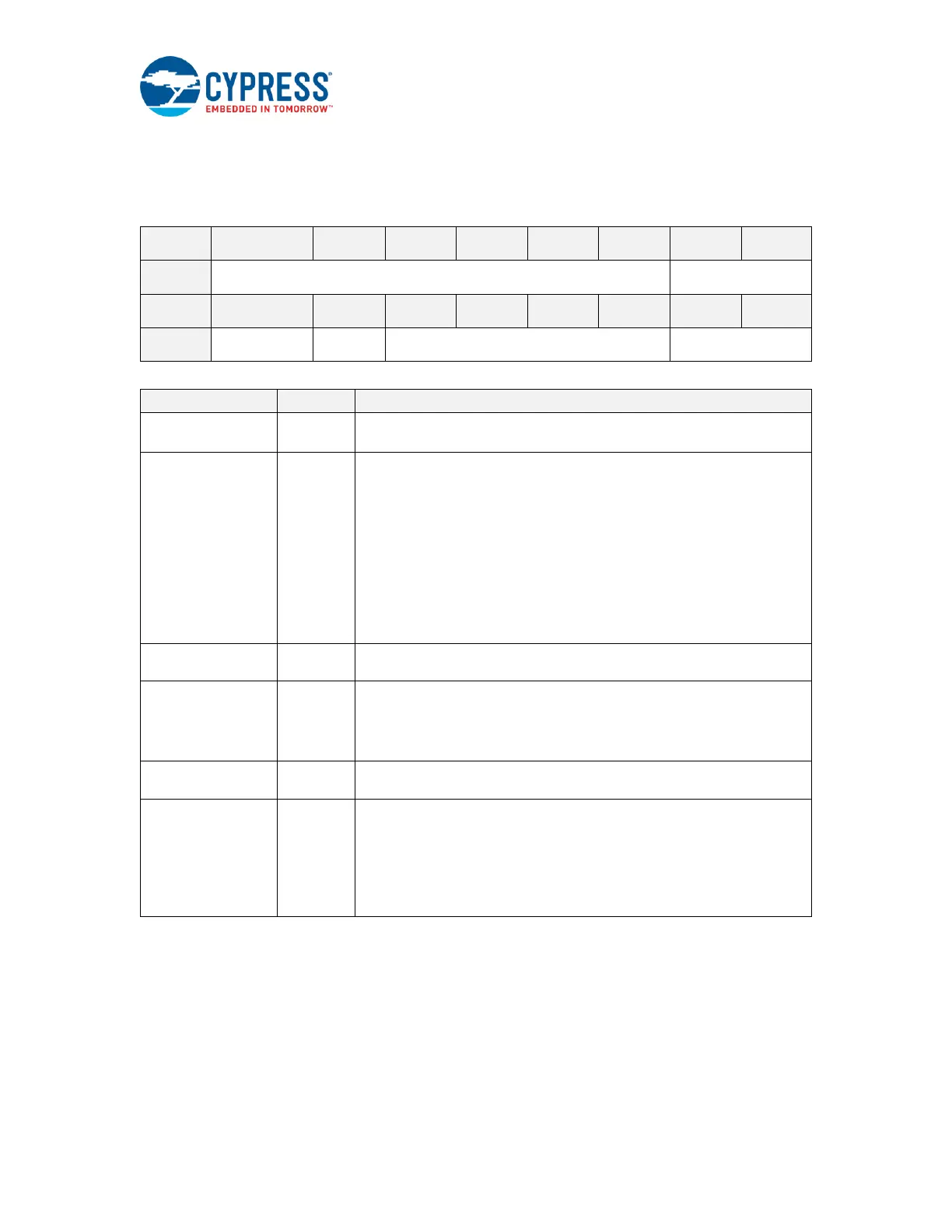

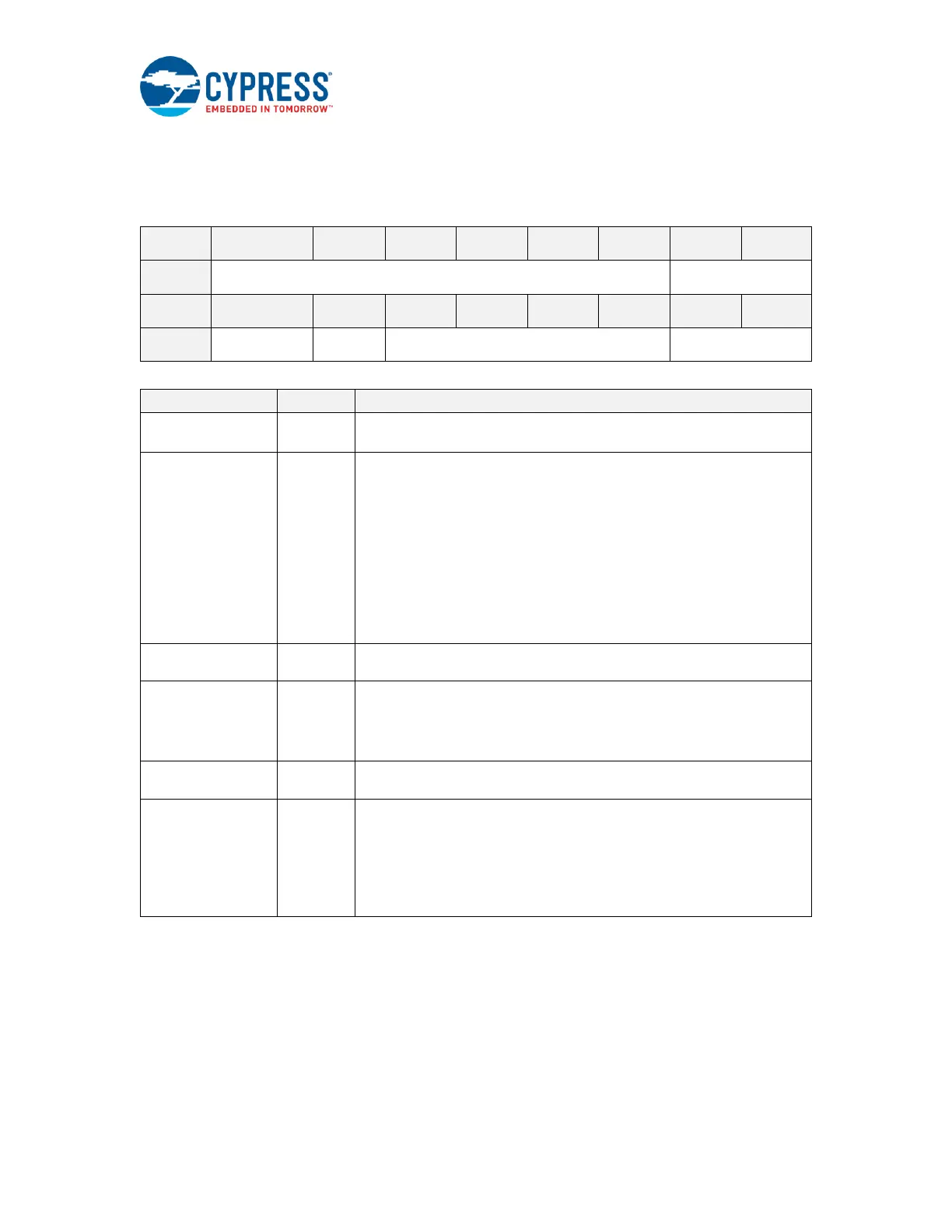

1.10.2 CX3_CONFIG_CTRL (Register Address: 0x0004)

This register controls number of data lanes and the output data mode for the MIPI CSI-2 block.

This register is set by the CyU3PMipicsiSetIntfParams() API and queried using the

CyU3PMipicsiQueryIntfParams() API.

RESERVED. Firmware must preserve their settings by reading them, changing

non-reserved bits, and re-writing them.

Data Mode Selection:

Sets the data mode for the data format selected using the DATA FORMAT bits

of the CX3_DATA_FMT register. The combination of DATA MODE and the

DATA FORMAT is used to select the output stream as defined in Table 3. The

DATA FORMAT setting determines the output data format, while the DATA

MODE setting determines the data packing and byte ordering for the

DATA TYPE as defined in Table 3.

2’b00: Mode 0

2’b01: Mode 1

2’b10: Mode 2

2’b11: Reserved

RESERVED. Firmware must preserve their settings by reading them, changing

non-reserved bits, and re-writing them.

Enable Parallel Output:

Enables parallel output from MIPI CSI-2 receiver block to fixed-function GPIF II.

0: Disable Parallel Output.

1: Enable Parallel Output

RESERVED. Firmware must preserve their settings by reading them, changing

non-reserved bits, and re-writing them.

MIPI CSI-2 Data Lane Selection:

Selects the number of data lanes to be used.

2’b00: 1 Data Lane

2’b01: 2 Data Lanes

2’b10: 3 Data Lanes

2’b11: 4 Data Lanes

Loading...

Loading...