Cypress EZ-USB CX3

EZ-USB® CX3 Technical Reference Manual, Doc. No. 001-91492 Rev. *B 8

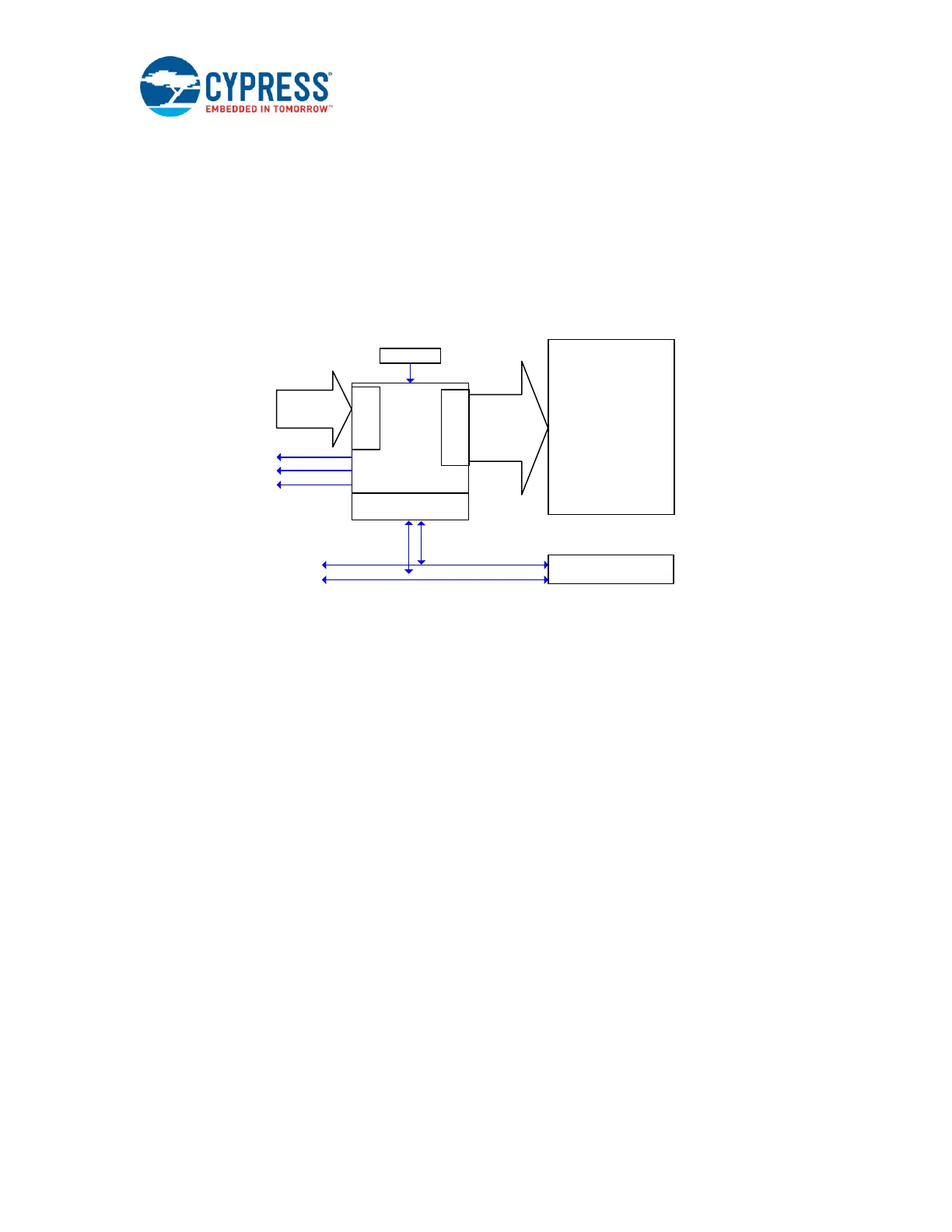

1.5 MIPI CSI-2 Block

The CX3 device has an integrated MIPI CSI-2 block, which is hard-wired to the GPIF II interface on one side

and provides a MIPI CSI-2 interface on the other side to interface to an image sensor that supports MIPI CSI-

2. The block supports up to four MIPI CSI-2 data lanes, and is capable of speeds up to 1 Gbps per lane. The

MIPI CSI-2 receiver is connected to a fixed-function GPIF II controller via an 8-, 16-, or 24-bit data bus, which

can be clocked up to 100 MHz. The maximum bandwidth that can be achieved is 2.4Gbps (i.e. 24 * 100 Mbps).

The MIPI CSI-2 block is configured over I

2

C and is available on the CX3 I

2

C bus at the 7-bit I

2

C slave address

7’b0000111.

Figure 5. CX3 MIPI CSI-2 Block

Loading...

Loading...