Cypress EZ-USB CX3

EZ-USB® CX3 Technical Reference Manual, Doc. No. 001-91492 Rev. *B 20

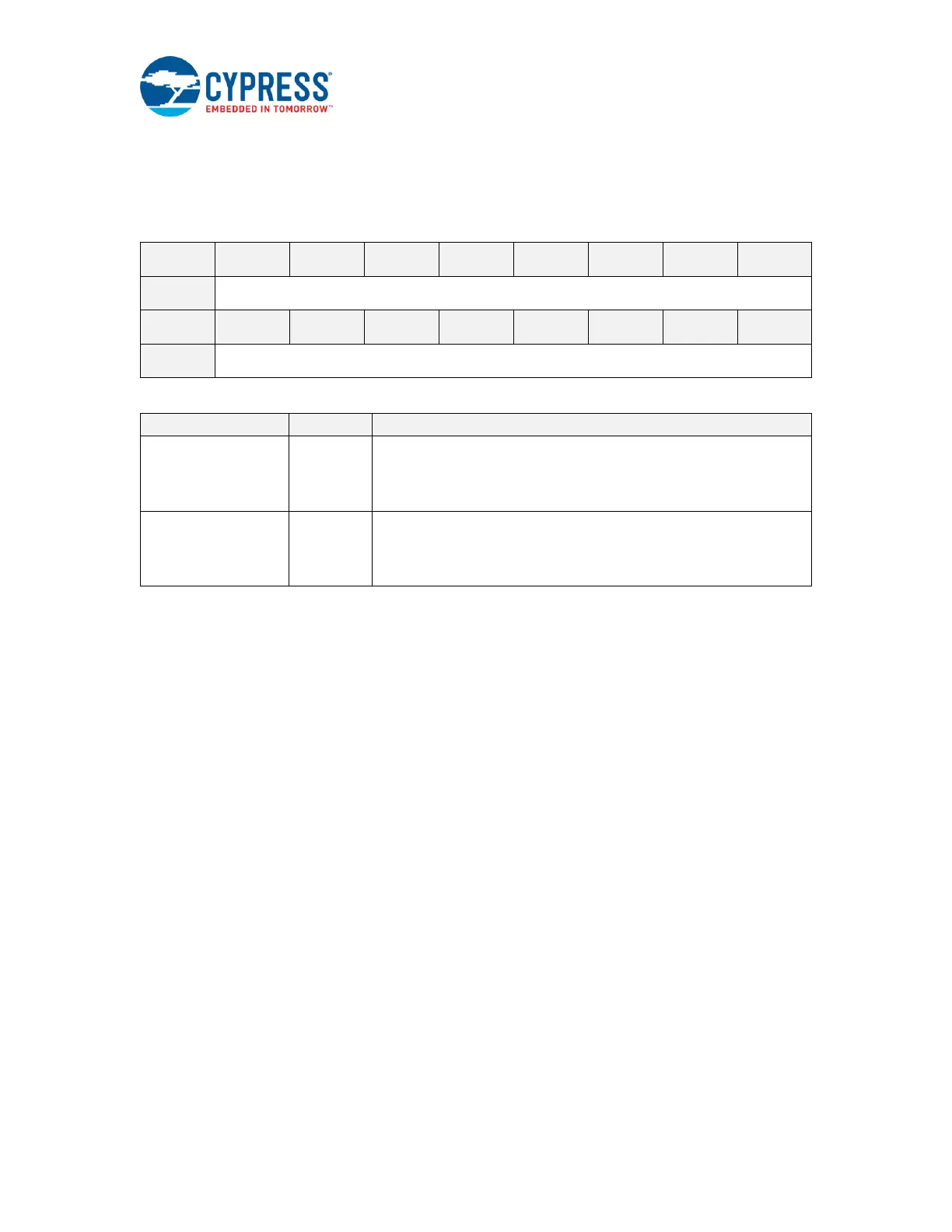

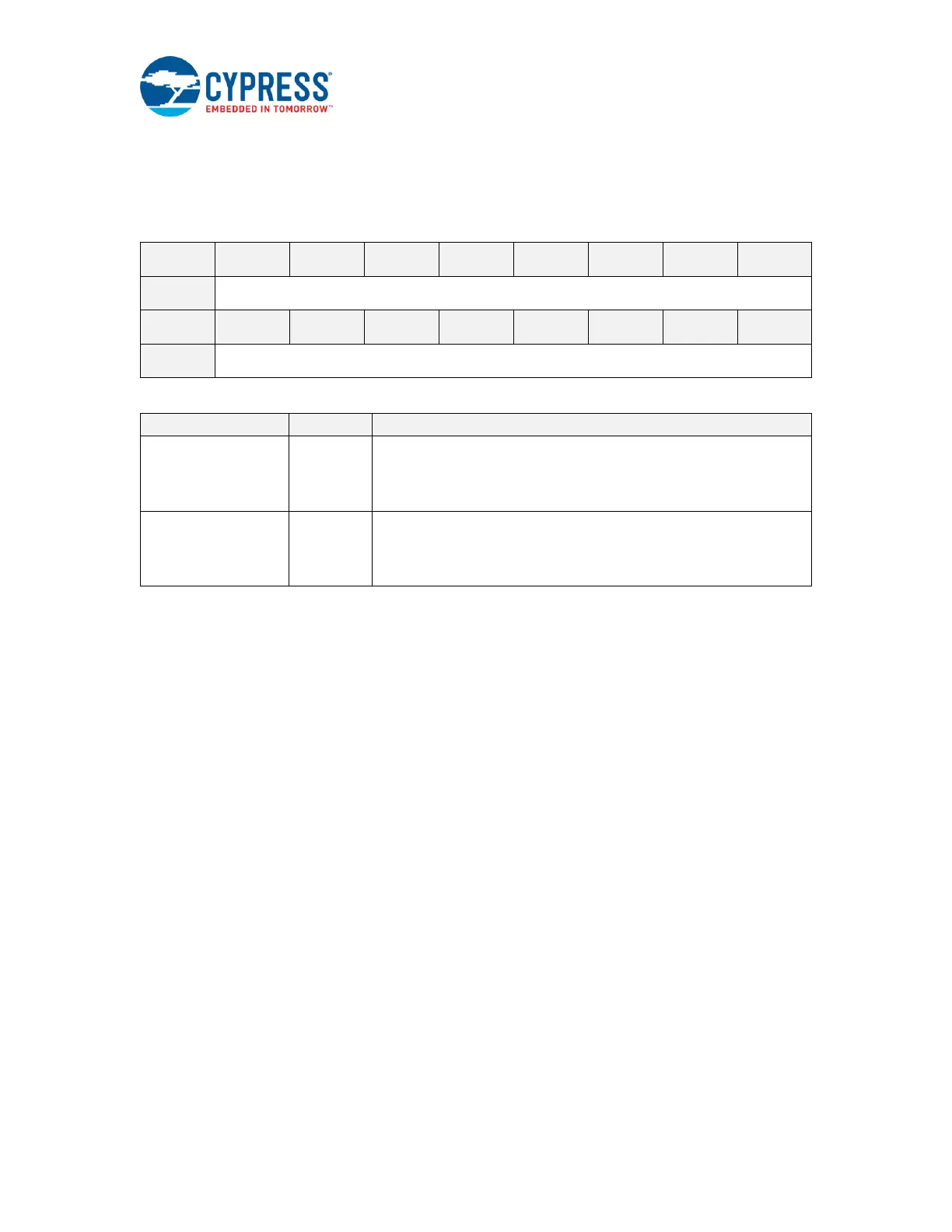

1.10.5 CX3_MCLK_CTRL (Register Address: 0x000C)

This register configures the MCLK divider and controls the Image Sensor Reference Clock (MCLK) output

from the MIPI CSI-2 block. Detailed information on calculating the MCLK value is provided in Section 1.7.5 .

This register is set by the CyU3PMipicsiSetIntfParams() API and queried using the

CyU3PMipicsiQueryIntfParams() API.

MCLK HIGH Time Count:

HIGH time count for the MCLK divider. See Section 1.7.5 for details on this

field.

MCLK is enabled only if MCLK HIGH and MCLK LOW are non-zero.

MCLK LOW Time Count:

LOW Time count for MCLK divider. See Section 1.7.5 for details on this

field.

MCLK Divider = (MCLK HIGH +1) + (MCLK LOW+1)

Loading...

Loading...