Cypress EZ-USB CX3

EZ-USB® CX3 Technical Reference Manual, Doc. No. 001-91492 Rev. *B 24

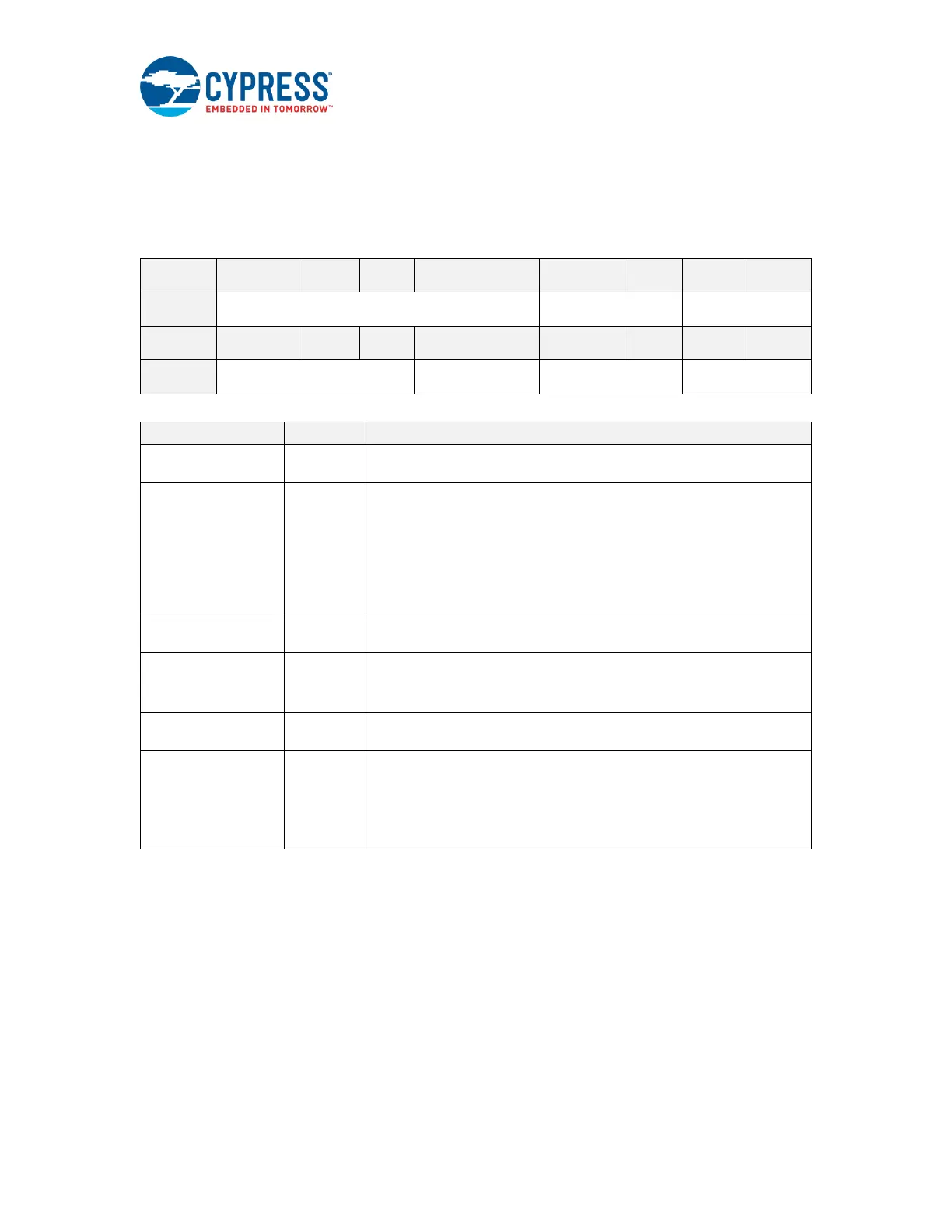

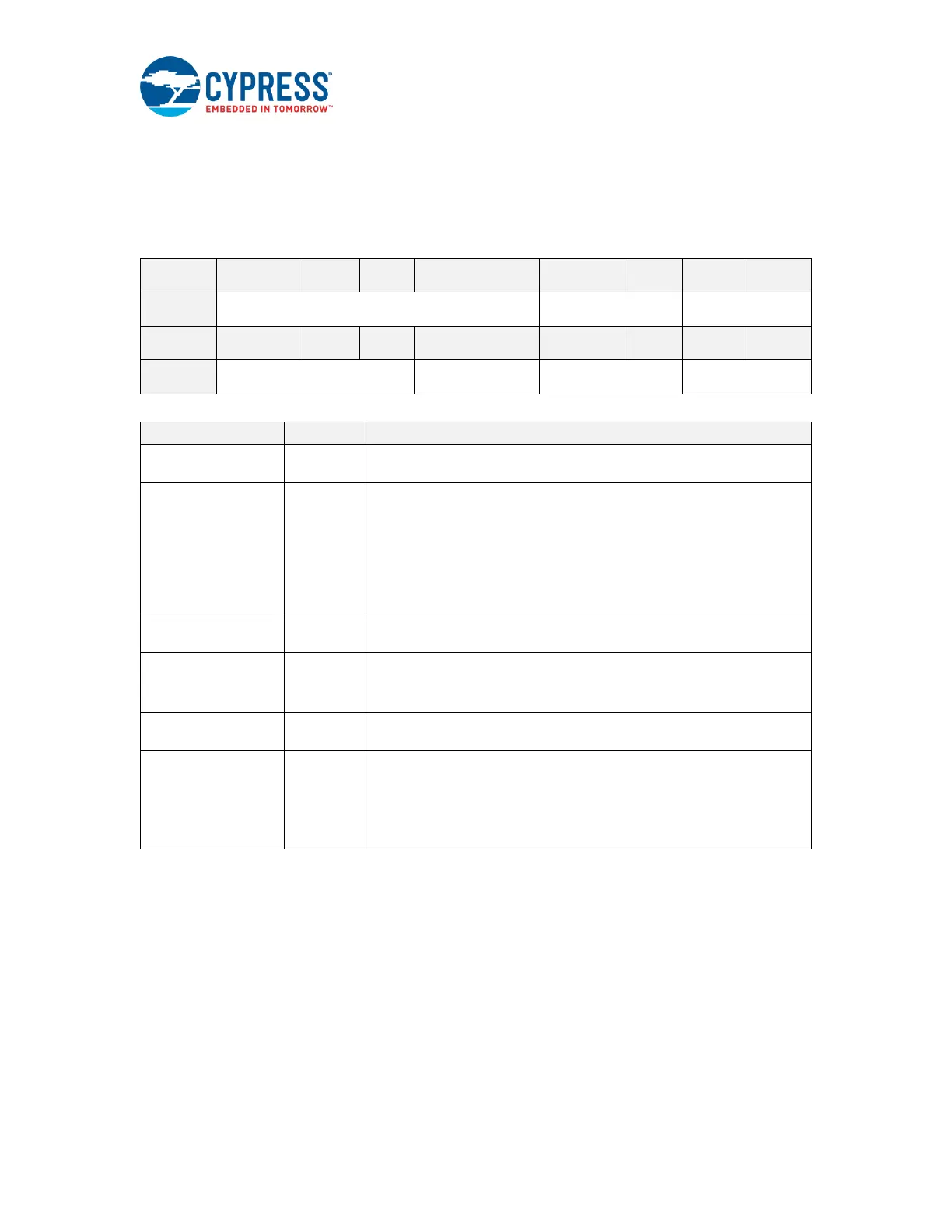

1.10.9 CX3_PLL_CTRL1 (Register Address: 0x0018)

This register configures the PLL clock on the MIPI CSI-2 block. Detailed description of how the PLL Clock is

generated based on the values from CX3_PLL_CTRL0 (Register Address: 0x0016) and CX3_PLL_CTRL1

(Register Address: 0x0018) is provided in Section 1.7.2 .

This register is set by the CyU3PMipicsiSetIntfParams() API and queried using the

CyU3PMipicsiQueryIntfParams() API.

RESERVED. Firmware must preserve their settings by reading them,

changing non-reserved bits, and re-writing them.

Frequency Range Selection:

Determines the PLL frequency range. See Section 1.7.2 for details on this

field.

2’b00: 500-1000 MHz PLL frequency

2’b01: 250-500 MHz PLL frequency

2’b10: 125-250 MHz PLL frequency

2’b11: 62.5-250 MHz PLL frequency

RESERVED. Firmware must preserve their settings by reading them,

changing non-reserved bits, and re-writing them.

Clock Enable:

0: Clocks on the MIPI CSI-2 block are switched off.

1: Clocks on the MIPI CSI-2 block are enabled (Normal Operation).

RESERVED. Firmware must preserve their settings by reading them,

changing non-reserved bits, and re-writing them.

Enable PLL Clock:

The setting to enable the PLL clock.

2’b00: PLL clock disabled

2’b11: PLL clock enabled (Normal Operation)

2b’01- 2b’10: RESERVED

Loading...

Loading...