Appendix

Appendix

User's Manual

BAB 740

7—10

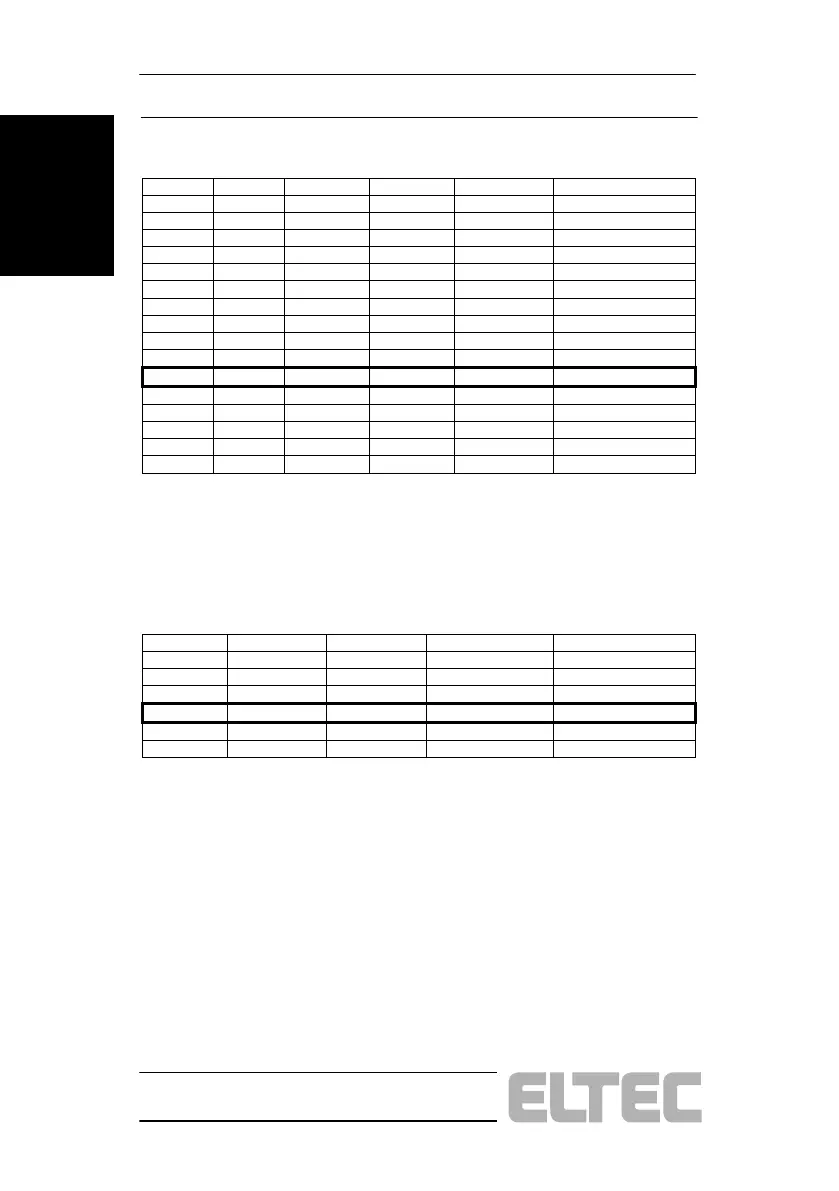

Table 40: CPU PLL Configuration (J103...J106)

J106 J105 J104 J103 Bus Mult. Bus Clock

short short short short x 7 25-33

short short short - - -

short short - short - -

short short - - bypass -

short - short short x 2 60-83

short - short - x 6,5 25-40

short - - short x 2,5 50-83

short - - - x 4,5 33-60

- short short short x 3 40-83

- short short - x 5,5 25-40

- short - short x 4 33-66 (default)

- short - - x 5 25-50

- - short short - -

- - short - x 6 25-40

- - - short x 3,5 40-75

- - - - off off

SMD jumper for factory use only

Note: Implementation specific settings; do not change!

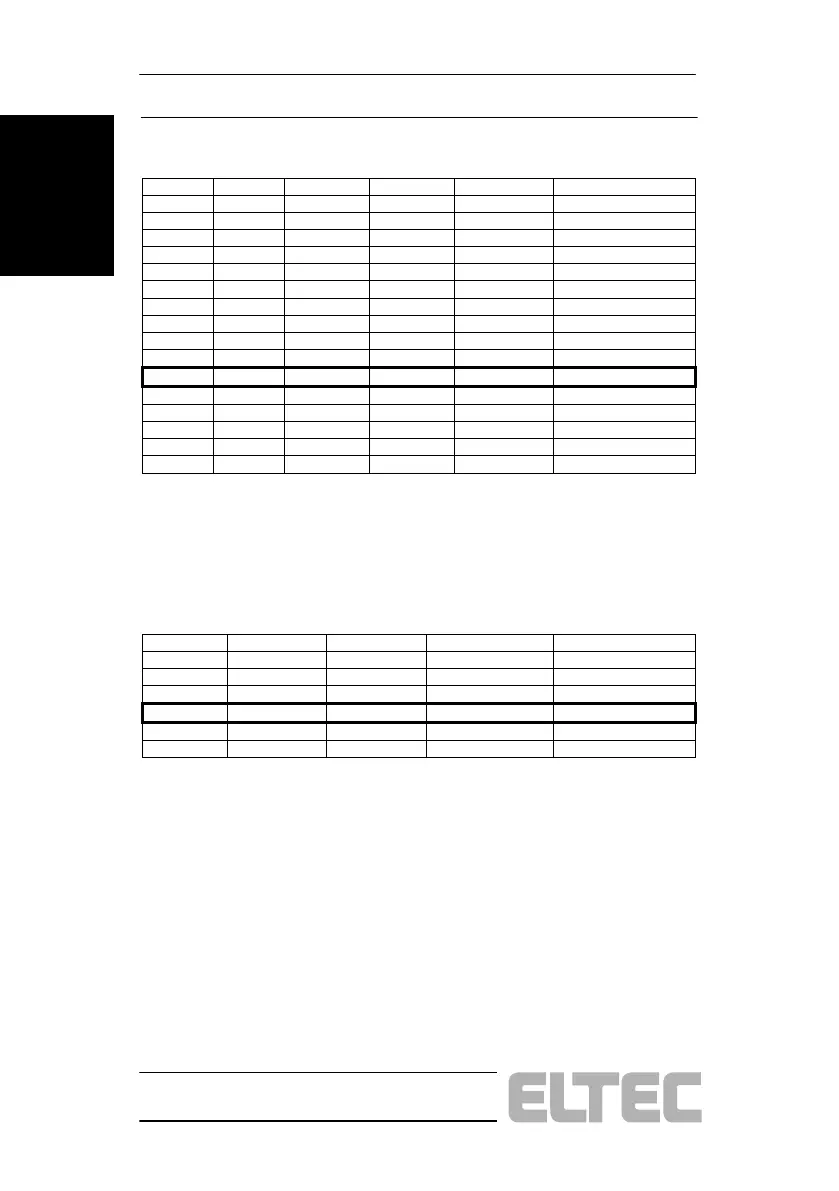

Table 41: System Clock (J111, J112, J113)

J111 J112 J113 CPU Bus Clock PCI Bus Clock

short short short 30 25

short short 60 30

short short 62,5 25

short 66 33 (default)

short short 75 37,5

short 83 33

SMD jumper for factory use only!

Note: Implementation specific settings; do not change!

Loading...

Loading...