Appendix

Appendix

User's Manual

BAB 740

7—11

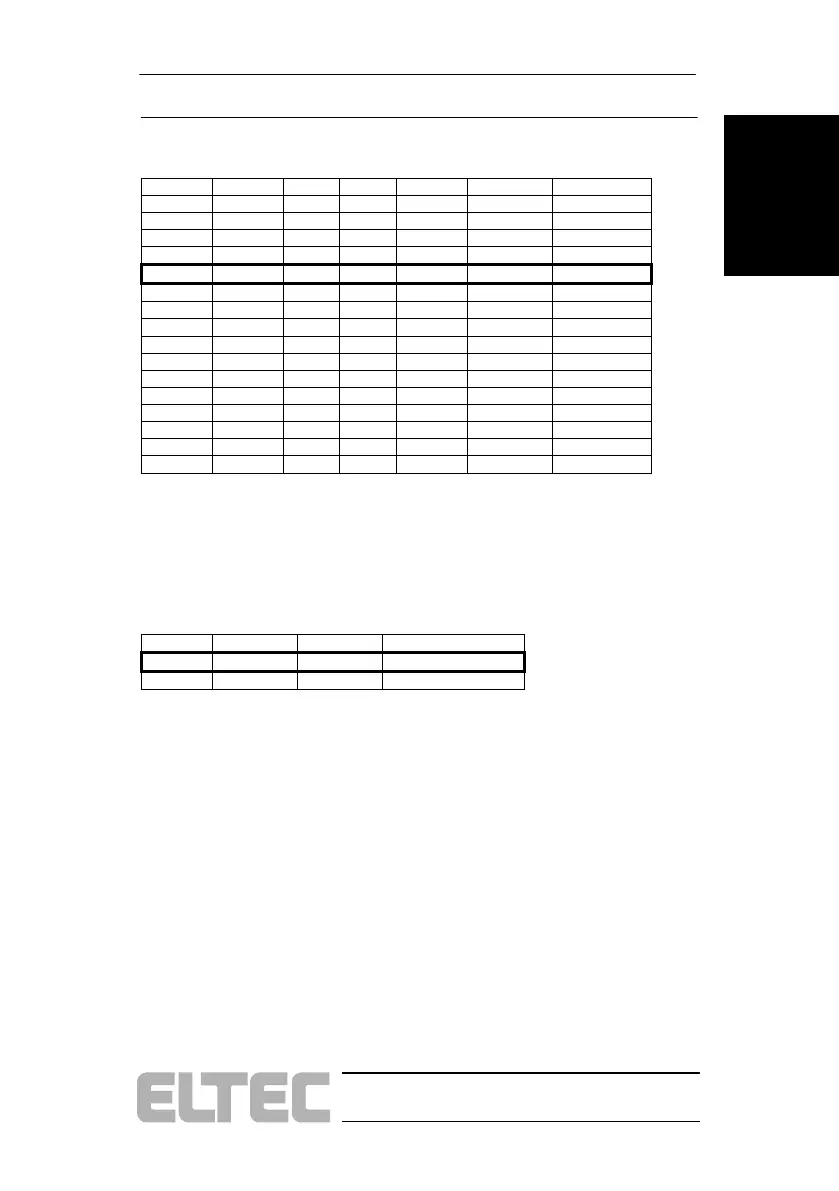

Table 42: MPC106 PLL Configuration (J110...J107)

J110 J109 J108 J107 Mult. Bus Clock PCI Clock

short short short short - - -

short short short - x 1 33 33

short short - short x 1 16-25 16-25

short short - - bypass - -

short - short short x 2 66 33 (default)

short - short - x 2 33-50 16-25

short - - short x 2,5 83 33

short - - - x 2,5 41-50 16-20

- short short short x 3 75-100 25-33

- short short - x 3 50 16

- short - short - - -

- short - - - - -

- - short short - - -

- - short - - - -

- - - short - - -

- - - - off - -

SMD jumper for factory use only

Note: Implementation specific settings; do not change!

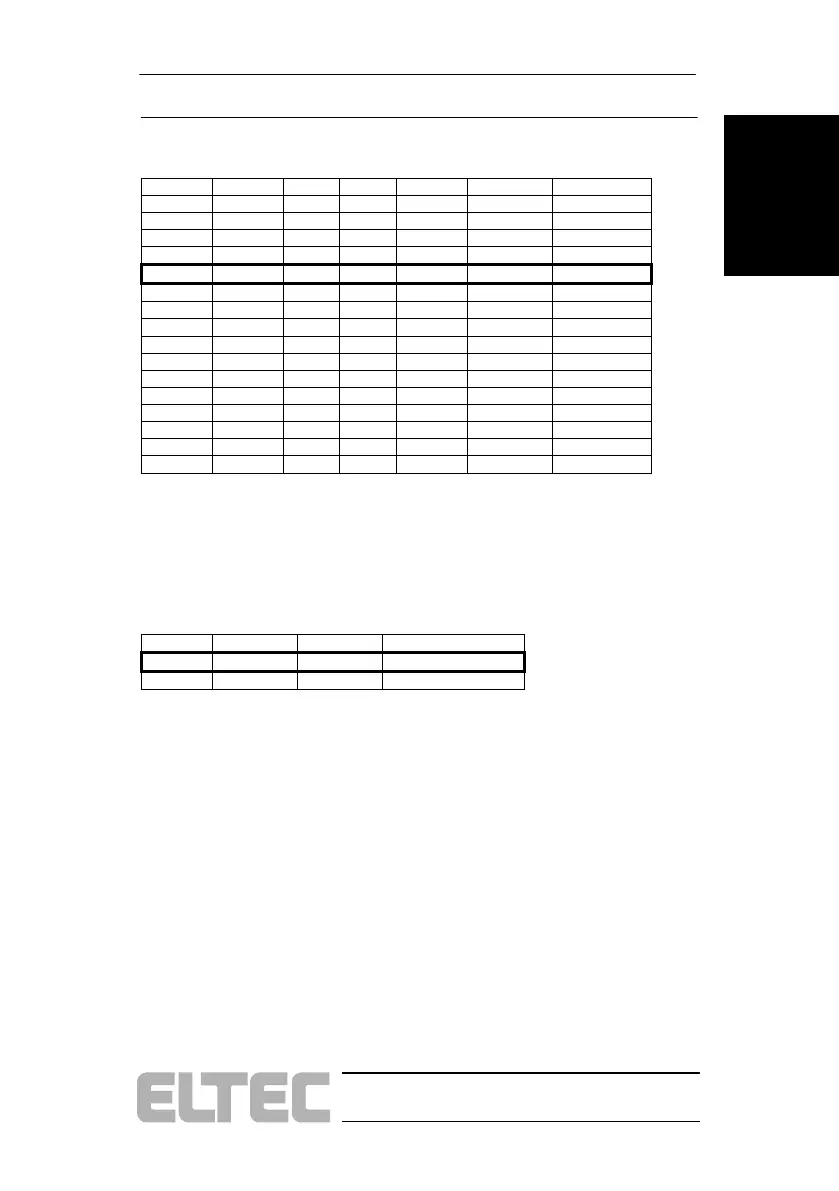

Table 43: Cache Size (J601, J602, J603)

J601 J602 J603 PCI Bus Clock

1-2 1-2 open 512 Cache (default)

2-3 2-3 short 256 Cache

SMD jumper for factory use only!

Note: Implementation specific settings; do not change!

Loading...

Loading...