8XC251SA, SB, SP, SQ USER’S MANUAL

A-16

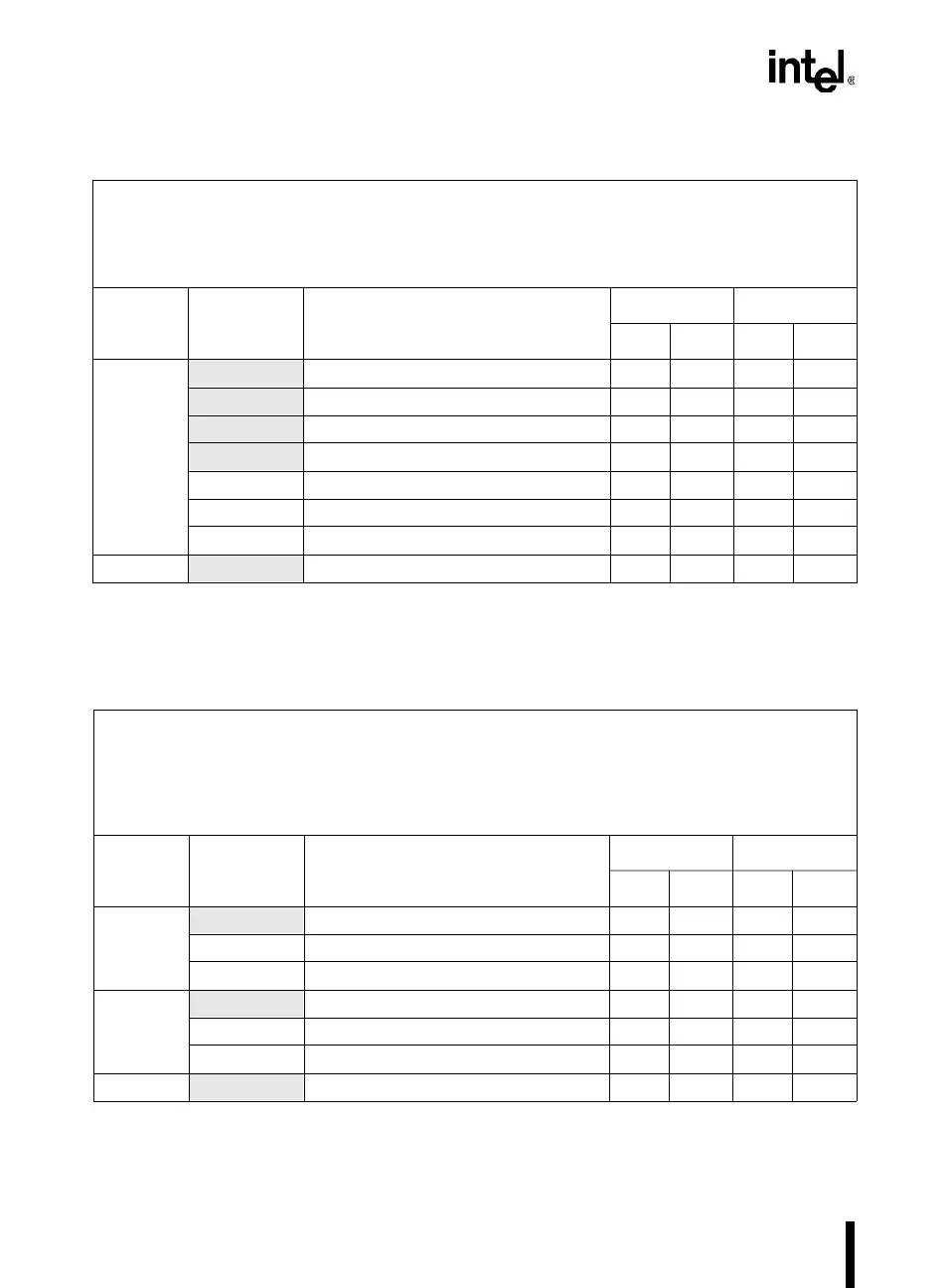

Table A-21. Summary of Increment and Decrement Instructions

Increment INC DPTR (DPTR) ← (DPTR) + 1

Increment INC byte byte ← byte + 1

Increment INC <dest>,<src> dest opnd ← dest opnd + src opnd

Decrement DEC byte byte ← byte – 1

Decrement DEC <dest>,<src> dest opnd ← dest opnd - src opnd

Mnemonic <dest>,<src> Notes

Binary Mode Source Mode

Bytes States Bytes States

INC;

DEC

A acc 1111

Rn Reg 1 1 2 2

dir8 Dir byte 2 2 (2) 2 2 (2)

@Ri Indir RAM 1 3 2 4

Rm,#short Byte reg by 1, 2, or 4 3 2 2 1

WRj,#short Word reg by 1, 2, or 4 3 2 2 1

DRk,#short Double word reg by 1, 2, or 4 3 4 2 3

INC

DPTR Data pointer 1 1 1 1

NOTES:

1. A shaded cell denotes an instruction in the MCS

®

51 architecture.

2. If this instruction addresses an I/O port (P

x

,

x

= 0–3), add 2 to the number of states.

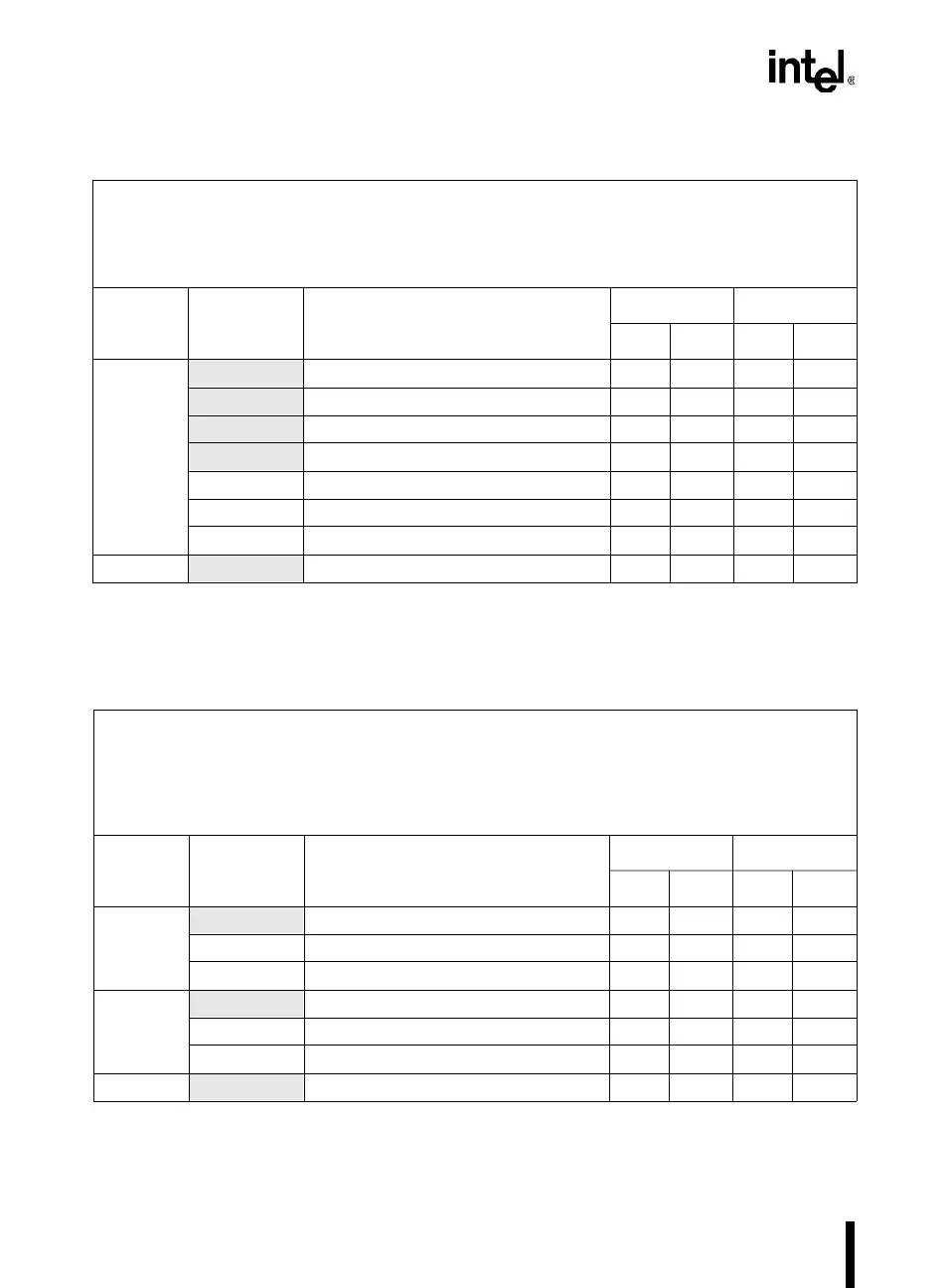

Table A-22. Summary of Multiply, Divide, and Decimal-adjust Instructions

Multiply MUL <reg1,reg2> (2)

MUL AB (B:A) = A x B

Divide DIV <reg1>,<reg2> (2)

DIV AB (A) = Quotient; (B) =Remainder

Decimal-adjust ACC DA A (2)

for Addition (BCD)

Mnemonic <dest>,<src> Notes

Binary Mode Source Mode

Bytes States Bytes States

MUL

AB Multiply A and B 1 5 1 5

Rmd,Rms Multiply byte reg and byte reg 3 6 2 5

WRjd,WRjs Multiply word reg and word reg 3 12 2 11

DIV

AB Divide A by B 1 10 1 10

Rmd,Rms Divide byte reg by byte reg 3 11 2 10

WRjd,WRjs Divide word reg by word reg 3 21 2 20

DA

A Decimal adjust acc 1 1 1 1

NOTES:

1. A shaded cell denotes an instruction in the MCS

®

51 architecture.

2. See section A.4, “Instruction Descriptions.”

Loading...

Loading...