Troubleshooting

2-28

Test 200.1 – A/D zero

Pass/Fail

No A/D communication and/or noisy A/D.

This test turns on Q328 by setting /HIV low and turns on Q525 by setting /DIVIDER

low. Switches U319 (/ZERO pulled low) and U318 (/X1 pulled low) are closed and

U808 is set for line cycle integration.

Common (ZERO) zeroes the A/D buffer (x1 gain). The zero is then applied to the A/D

converter. The A/D is triggered until the Charge Balance (CB) counts are the same. The

value is then stored and compared to a zero-by-design CB value. Final Slope (FS)

counts are also stored. If the A/D cannot make this measurement, the test will fail.

U808 (not communicating with the digital section) and most any component in A/D

circuitry.

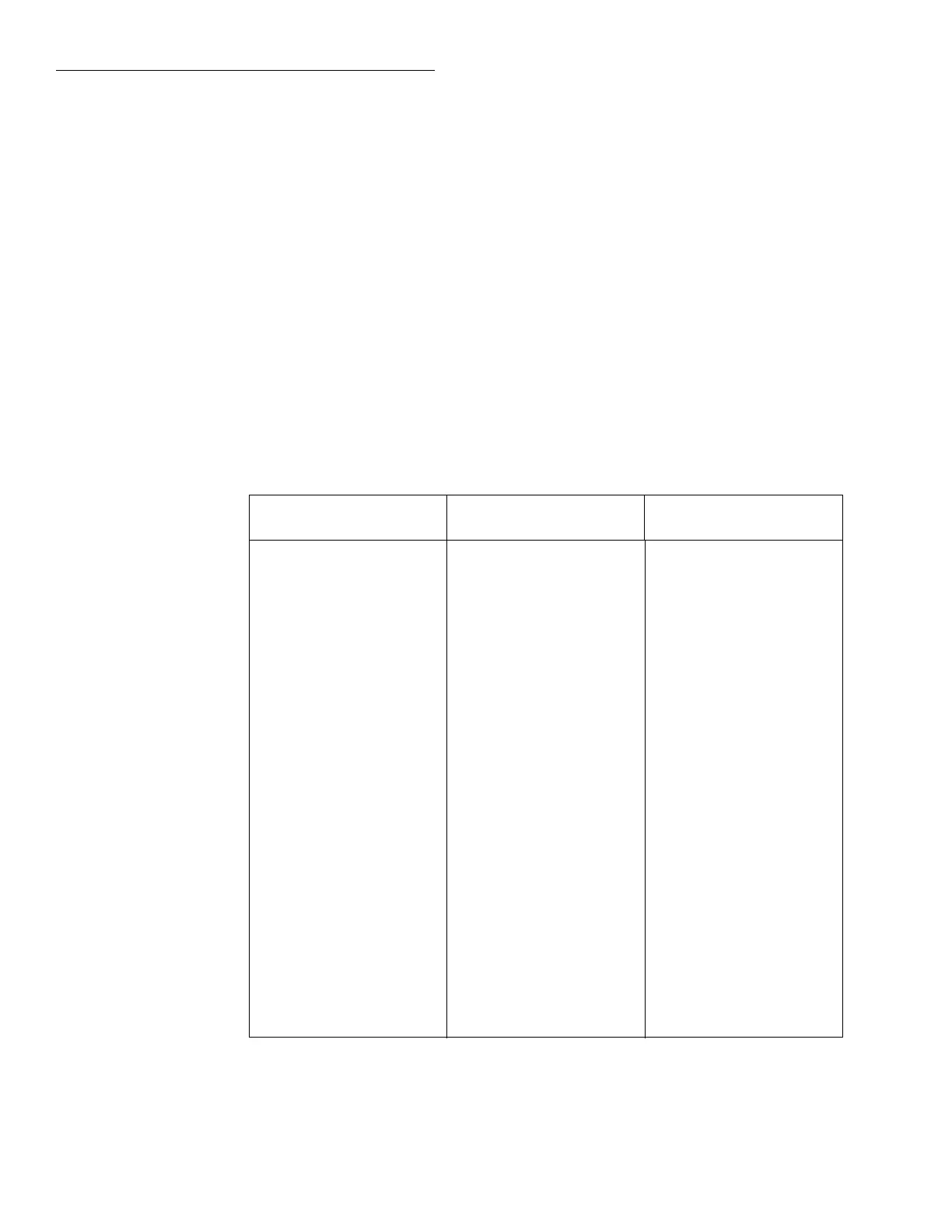

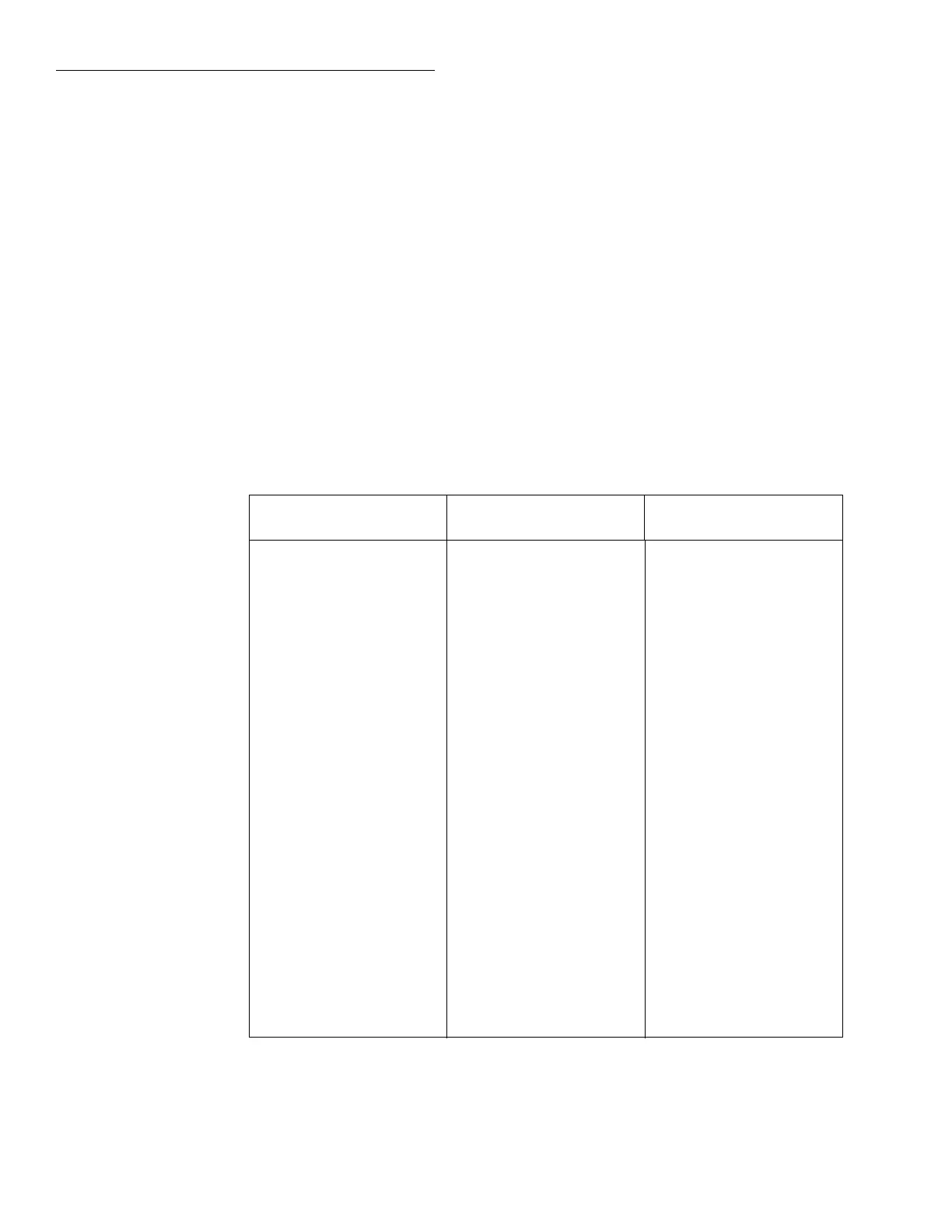

DC_STB

Registers

R1_STB

Registers

R2_STB

Registers

U801 Q1: 0

Q2: 1

Q3: 1

Q4: 1

Q5: 1

Q6: 0

Q7: 0

Q8: 0

U307 Q1: 1

Q2: 1

Q3: 0

Q4: 1

Q5: 1

Q6: 1

Q7: 1

Q8: 1

U505 Q1: 0

Q2: 0

Q3: 1

Q4: 0

Q5: 0

Q6: 0

Q7: 0

Q8: 0

U800 Q1: 1

Q2: 1

Q3: 0

Q4: 0

Q5: 0

Q6: 0

Q7: 1

Q8: 1

U305 Q1: 1

Q2: 0

Q3: 1

Q4: 0

Q5: 0

Q6: 0

Q7: 1

Q8: 1

U500 Q1: 1

Q2: 1

Q3: 0

Q4: 1

Q5: 1

Q6: 1

Q7: 1

Q8: 1

U300 Q1: 1

Q2: 1

Q3: 1

Q4: 1

Q5: 1

Q6: 1

Q7: 0

Q8: 0

U302 Q1: 1

Q2: 1

Q3: 1

Q4: 1

Q5: 1

Q6: 1

Q7: 1

Q8: 0

U530 Q1: 0

Q2: 0

Q3: 0

Q4: 0

Q5: 0

Q6: 0

Q7: 0

Q8: 1

U303 Q1: 0

Q2: 1

Q3: 1

Q4: 1

Q5: 1

Q6: 1

Q7: X

Q8: X

U501 Q1: 1

Q2: 1

Q3: 0

Q4: 1

Q5: 1

Q6: 1

Q7: X

Q8: X

Note: Tables 2-10 through 2-12 provide functional descriptions of the register bits.

Type

Failure analysis

Description

High suspect

components

Bit pattern

Loading...

Loading...