A3V56S30FTP (DIGITAL : U2604,U2605 )

A3V56S30FTP

Pin Function

A3V56S30FTP

A3V56S40FTP

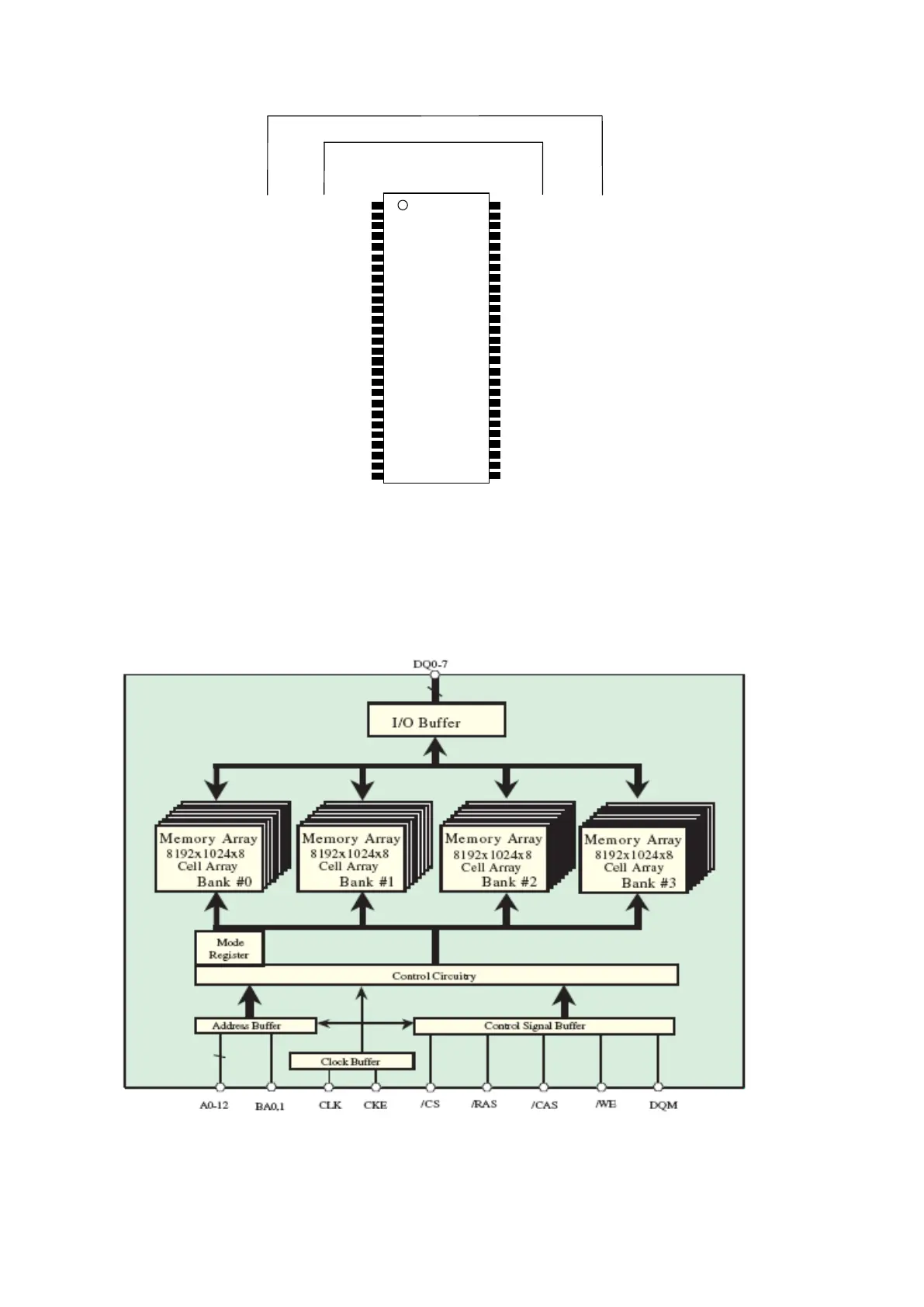

256M Single Data Rate Synchronous DRAM

Revision 1.1 Mar., 2010

Page 2 / 39

CLK : Master Clock DQM : Output Disable / Write Mask (A3V56S30FTP)

CKE : Clock Enable DQMU,L : Output Disable / Write Mask (A3V56S40FTP)

/CS : Chip Select A0-12 : Address Input

/RAS : Row Address Strobe BA0,1 : Bank Address

/CAS : Column Address Strobe Vdd : Power Supply

/WE : Write Enable VddQ : Power Supply for Output

DQ0-7 : Data I/O (A3V56S30FTP) Vss : Ground

DQ0-15 : Data I/O (A3V56S40FTP) VssQ : Ground for Output

BA0

BA1

Vdd

DQ0

VddQ

DQ1

DQ2

VssQ

DQ3

DQ4

VddQ

DQ5

DQ6

VssQ

DQ7

Vdd

DQML

/WE

/CAS

/RAS

/CS

10(AP)

2

3

Vdd

0

1

Vdd

DQ0

VddQ

NC

DQ1

VssQ

NC

DQ2

VddQ

NC

DQ3

VssQ

NC

Vdd

NC

/WE

/CAS

/RAS

/CS

BA0

BA1

10(AP)

2

3

Vdd

0

1

DQM

CKE

Vss

DQ15

VssQ

DQ14

DQ13

VddQ

DQ12

DQ11

VssQ

DQ10

DQ9

VddQ

DQ8

Vss

NC

DQMU

CLK

CKE

12

11

8

7

6

5

4

Vss

9

Vss

DQ7

VssQ

NC

DQ6

VddQ

NC

DQ5

VssQ

NC

DQ4

VddQ

NC

Vss

NC

CLK

12

11

8

7

6

5

4

Vss

9

PIN CONFIGURATION (TOP VIEW)

PIN CONFIGURATION

(TOP VIEW)

x16

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

23 32

24 31

25 30

26 29

27 28

A3V56S30FTP

A3V56S40FTP

256M Single Data Rate Synchronous DRAM

Revision 1.1 Mar., 2010

Page 3 / 39

Note:This figure shows the A3V56S30FTP

The A3V56S40FTP configuration is 8192x512x16 of cell array and DQ0-15

Type Designation Code

A 3V 56 S40F TP-G6

Speed Grade 75: 133MHz@CL=3

7: 143MHz@CL=3

6: 166MHz@CL=3

G: Green

Package Type TP:TSOP (II)

Process Generation

Function Reserved for Future Use

Organization 2

n

3:x8, 4:x16

SDR Synchronous DRAM

Density 56:256M bits

Interface V:LVTTL

Memory Style (DRAM)

Zentel DRAM

158

Loading...

Loading...