30 CONTENTS

LED Name Description

D9 FPGA state Green: FPGA is loaded

D10 PCI Express® x4 connection state Green: No problem with connection (PCI Express host supports 4

lanes)

D24 PCI Express® x1 connection state Green: No problem with connection (PCI Express host supports 1

lanes)

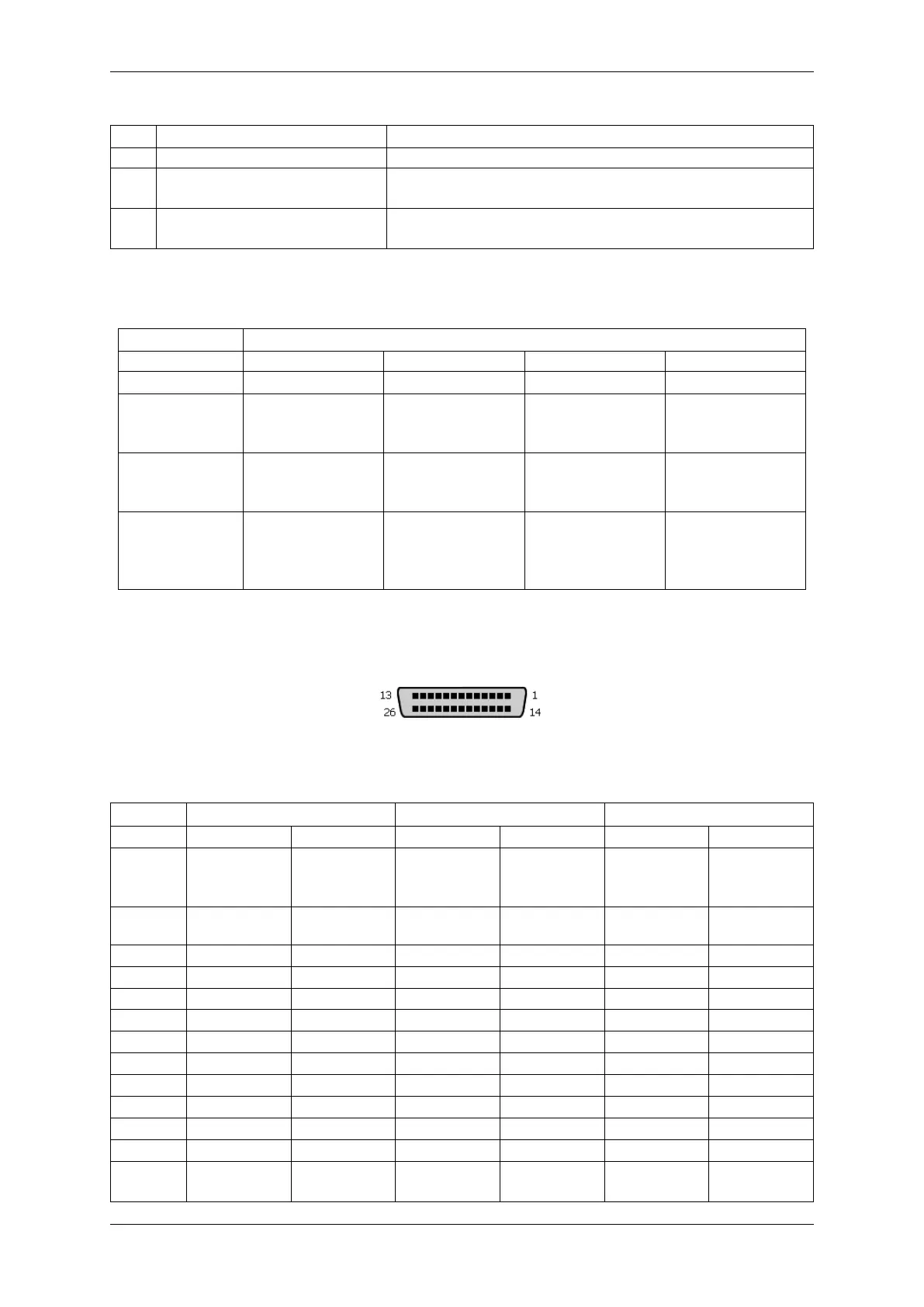

8.1.2.2 Use of J1..J4

Connector usage mvHYPERION

-CLb -CLe -CLm -CLf

J1 Camera 1 (BASE 1) Camera 1 (BASE 1) Camera 1 (BASE 1) Camera 1 (BASE 1)

J2 - Camera 1 (MEDI←-

UM 1) or camera 2

(BASE 2)

Camera 1 (MEDI←-

UM 1) or camera 2

(BASE 2)

Camera 1 (MEDI←-

UM 1) or camera 1

(FULL 1)

J3 Camera 1 trigger

/ sync / strobe /

power connector

Camera 1 trigger

/ sync / strobe /

power connector

Camera 1 trigger

/ sync / strobe /

power connector

Camera 1 trigger

/ sync / strobe /

power connector

J4 - Camera 2 trigger

/ sync / strobe /

power connector

Camera 2 trigger

/ sync / strobe /

power connector

Additional con-

nector with trigger

/ sync / strobe /

power

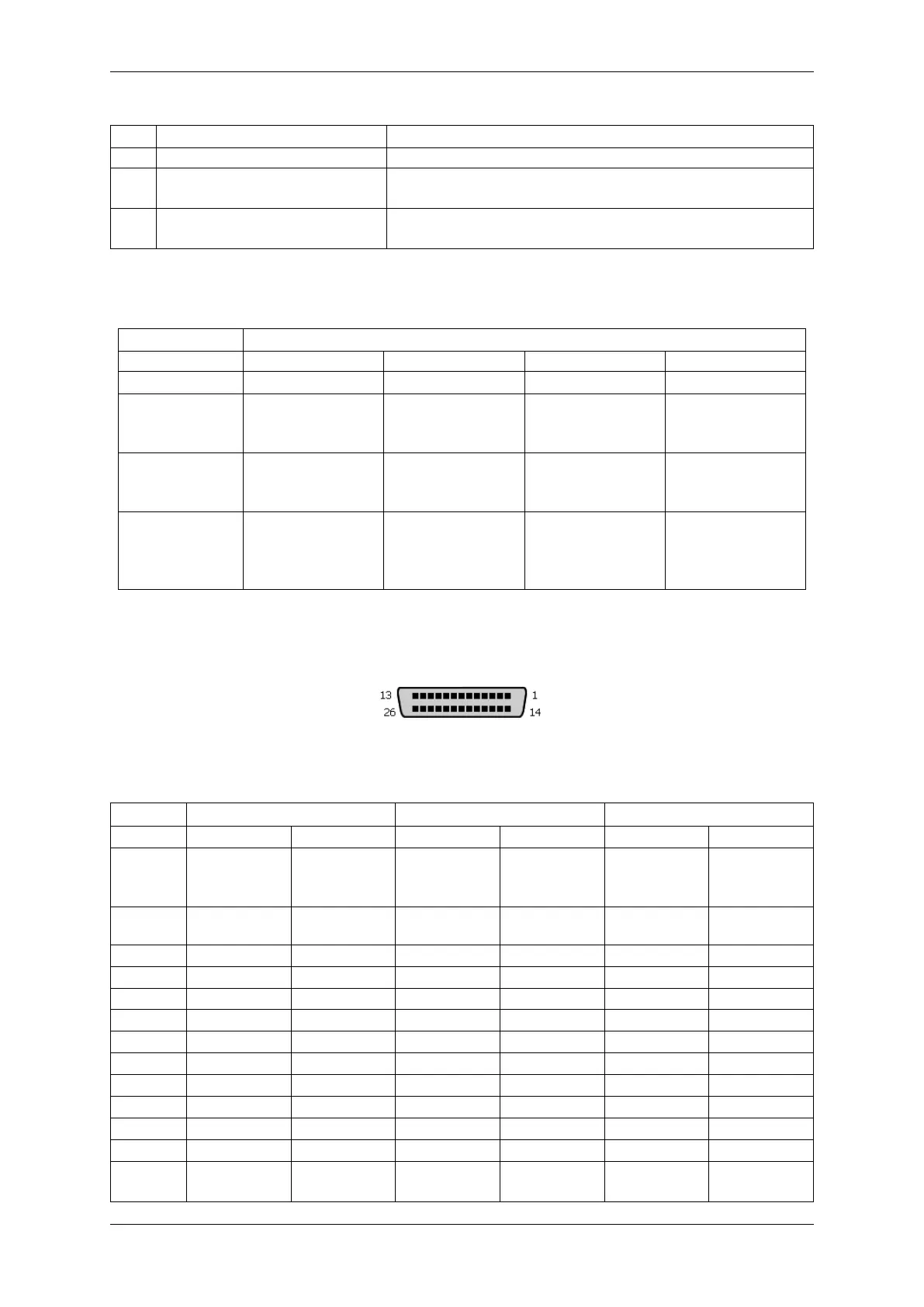

8.1.2.3 Pinning J1/J2 (CL configuration)

Figure 7: Mini CameraLink connector (female)

Pin J1/J2 (used as) BASE (used as) MEDIUM (used as) FULL

Signal Type Signal Type Signal Type

1 Internal

shield or

Power

PoCL (p. 120)

(+12V or

Ground)

Internal

shield or

Power

PoCL (p. 120)

(+12V or

Ground)

Internal

shield or

Power

PoCL (p. 120)

(+12V or

Ground)

14 Internal

shield

Ground Internal

shield

Ground Internal

shield

Ground

25 X0- Input 1- Y0- Input 1- Y0- Input 1-

12 X0+ Input 1+ Y0+ Input 1+ Y0+ Input 1+

24 X1- Input 2- Y1- Input 2- Y1- Input 2-

11 X1+ Input 2+ Y1+ Input 2+ Y1+ Input 2+

23 X2- Input 3- Y2- Input 3- Y2- Input 3-

10 X2+ Input 3+ Y2+ Input 3+ Y2+ Input 3+

22 Xclk- Input 4- Yclk- Input 4- Yclk- Input 4-

9 Xclk+ Input 4+ Yclk+ Input 4+ Yclk+ Input 4+

21 X3- Input 5- Y3- Input 5- Y3- Input 5-

8 X3+ Input 5+ Y3+ Input 5+ Y3+ Input 5+

20 SerTC+ Output 6+ Not used - - Not used, In-

put 6+

MATRIX VISION GmbH

Loading...

Loading...