ZLR964222L Line Module User Guide

45

Microsemi Corporation Confidential and Proprietary

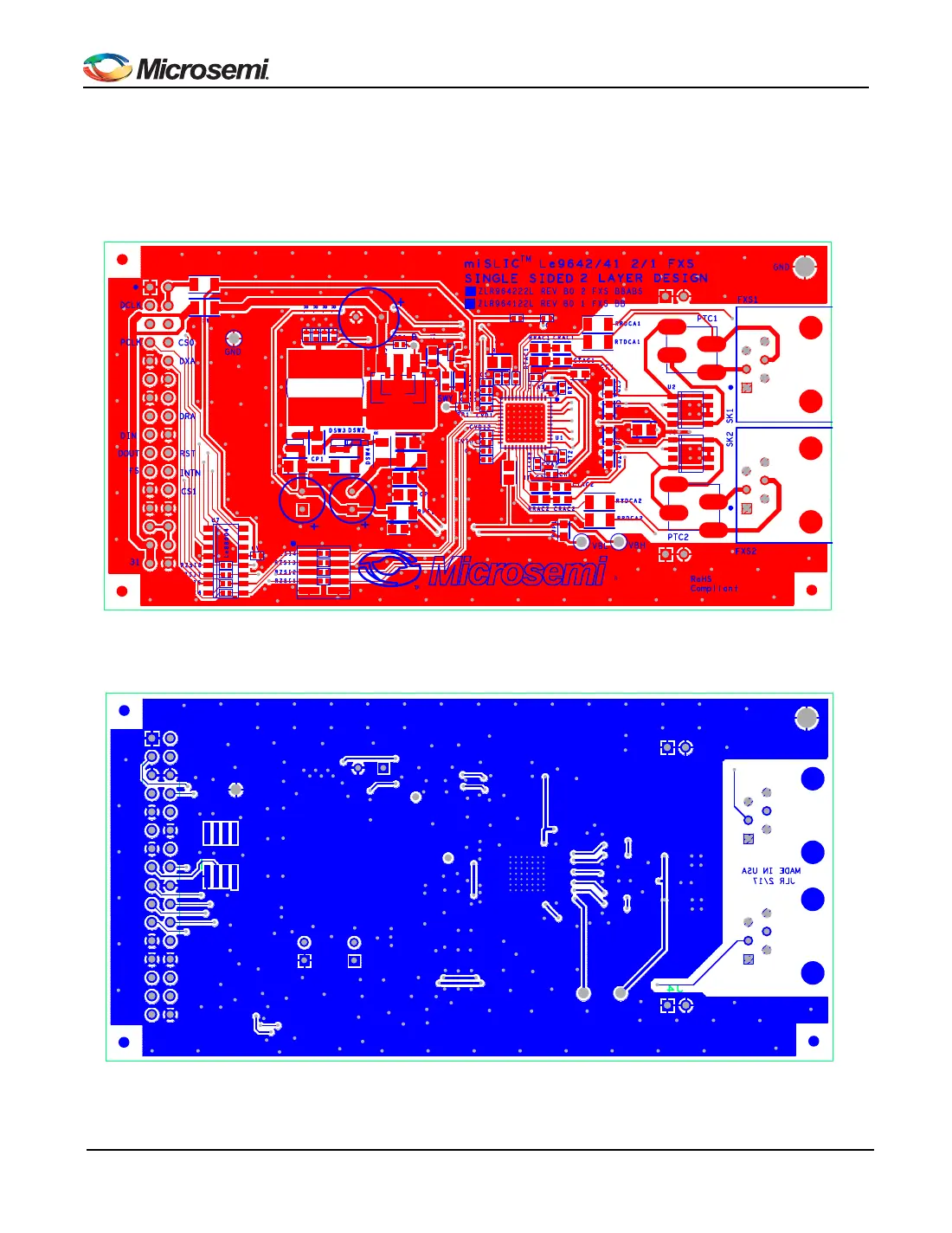

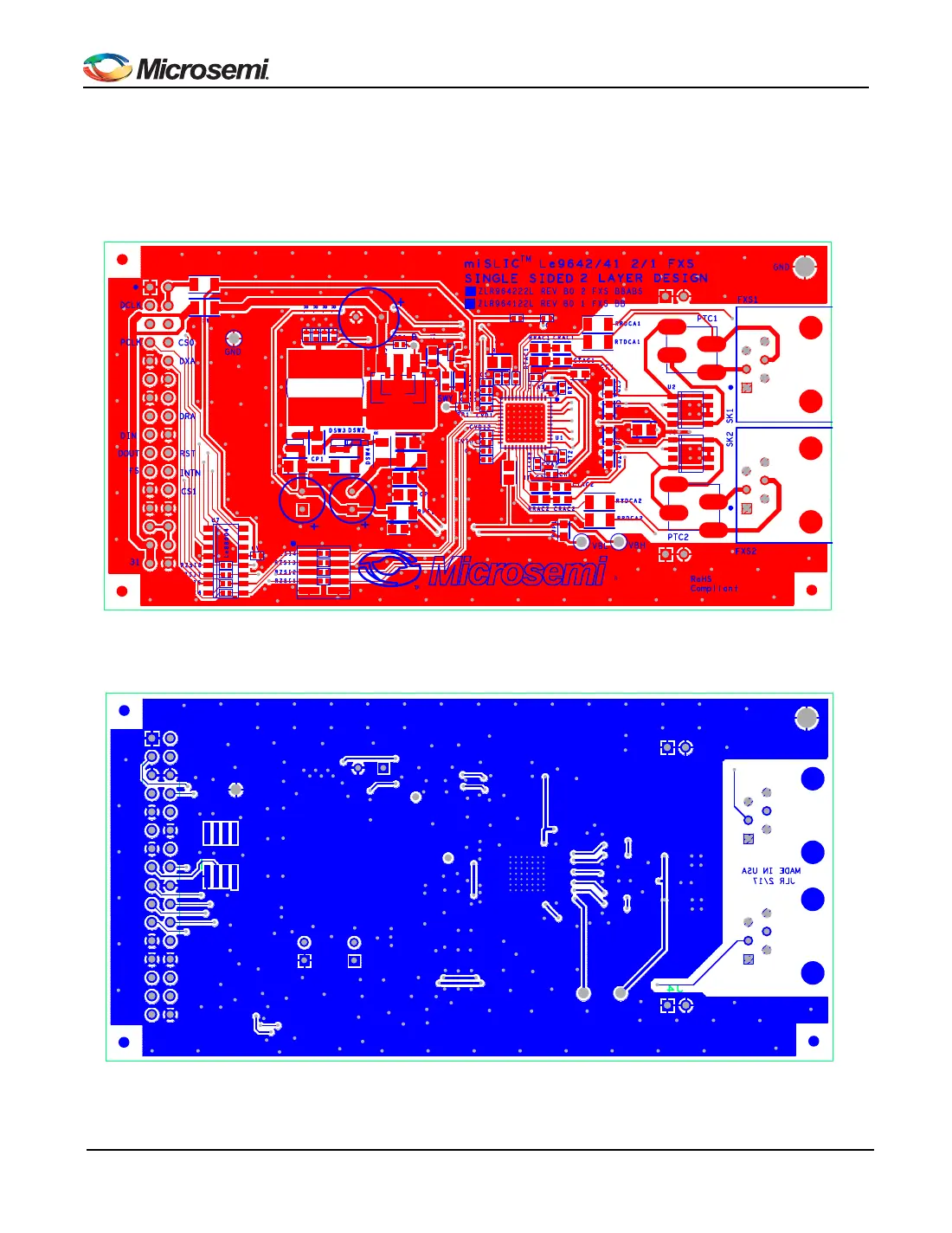

7.5 ZLR964222L Rev B0 Layout Plots

Plots of the layout of the ZLR964222L Line Module are provided in this section. This layout is available in Cadence

Allegro .brd (V16.5) format upon request. The gerber files are also available.

Figure 28 - Top Etch and Silk Screen

Figure 29 - Bottom Etch and Silk Screen

Loading...

Loading...