501

FX3G/FX3U/FX3GC/FX3UC Series

Programming Manual - Basic & Applied Instruction Edition

18 Floating Point – FNC110 to FNC139

18.11 FNC123 – EDIV / Floating Point Division

11

FNC30-FNC39

Rotation and

Shift

12

FNC40-FNC49

Data Operation

13

FNC50-FNC59

High-Speed

Processing

14

FMC60-FNC69

Handy

Instruction

15

FNC70-FNC79

External FX I/O

Device

16

FNC80-FNC89

External FX

Device

17

FNC100-FNC109

Data

Transfer 2

18

FNC110-FNC139

Floating Point

19

FNC140-FNC149

Data

Operation 2

20

FNC150-FNC159

Positioning

Control

18.11 FNC123 – EDIV / Floating Point Division

Outline

This instruction executes division of two binary floating point.

→ For program examples of floating point operations, refer to Section 12.10.

→ For handling of floating point, refer to Subsection 5.1.3.

→ For flag operations, refer to Subsection 6.5.2.

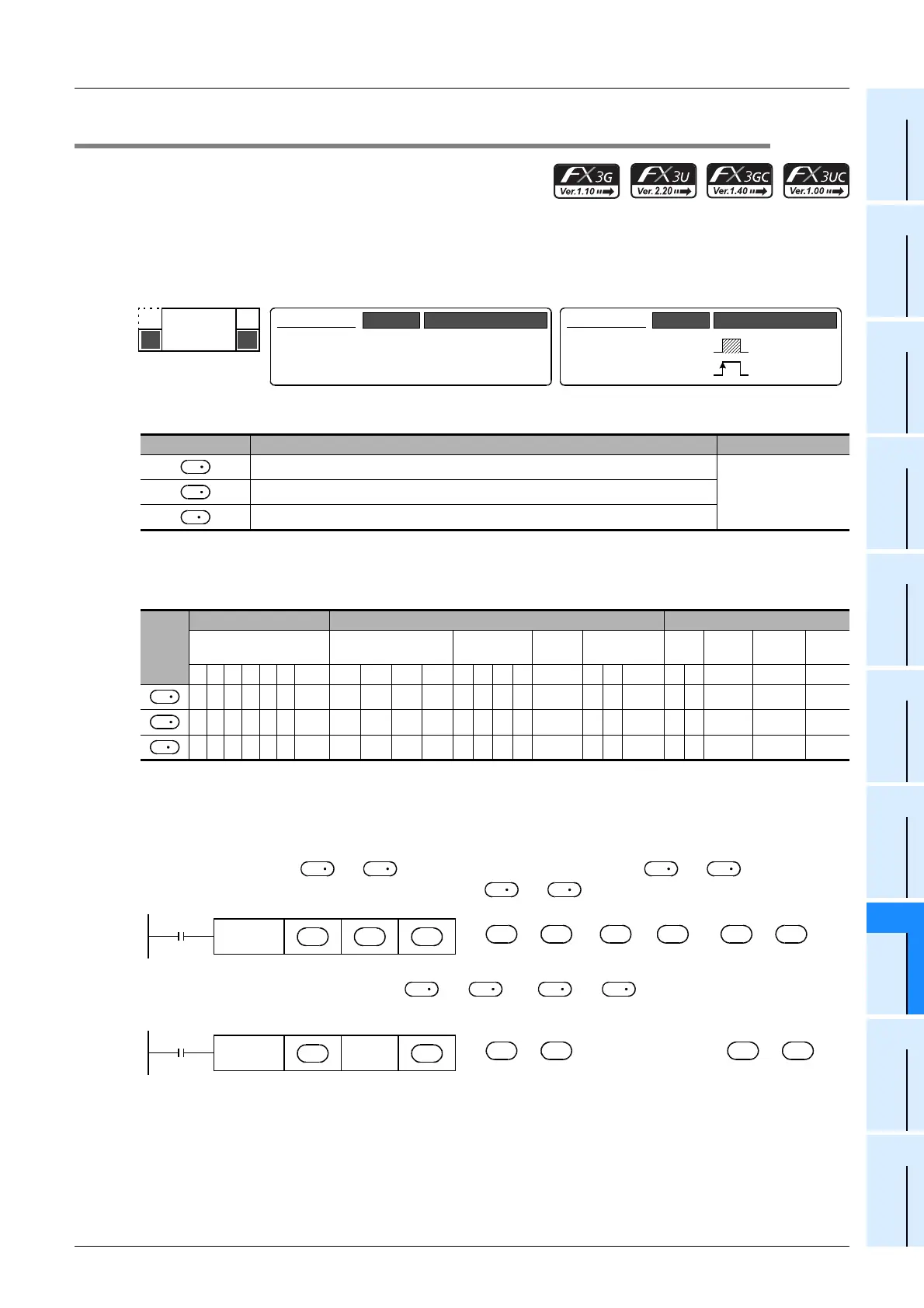

1. Instruction format

2. Set data

*1. When a constant (K or H) is specified, it is automatically converted into binary floating point (real number)

when the instruction is executed.

3. Applicable devices

S: This function is supported only in FX3U/FX3UC PLCs.

Explanation of function and operation

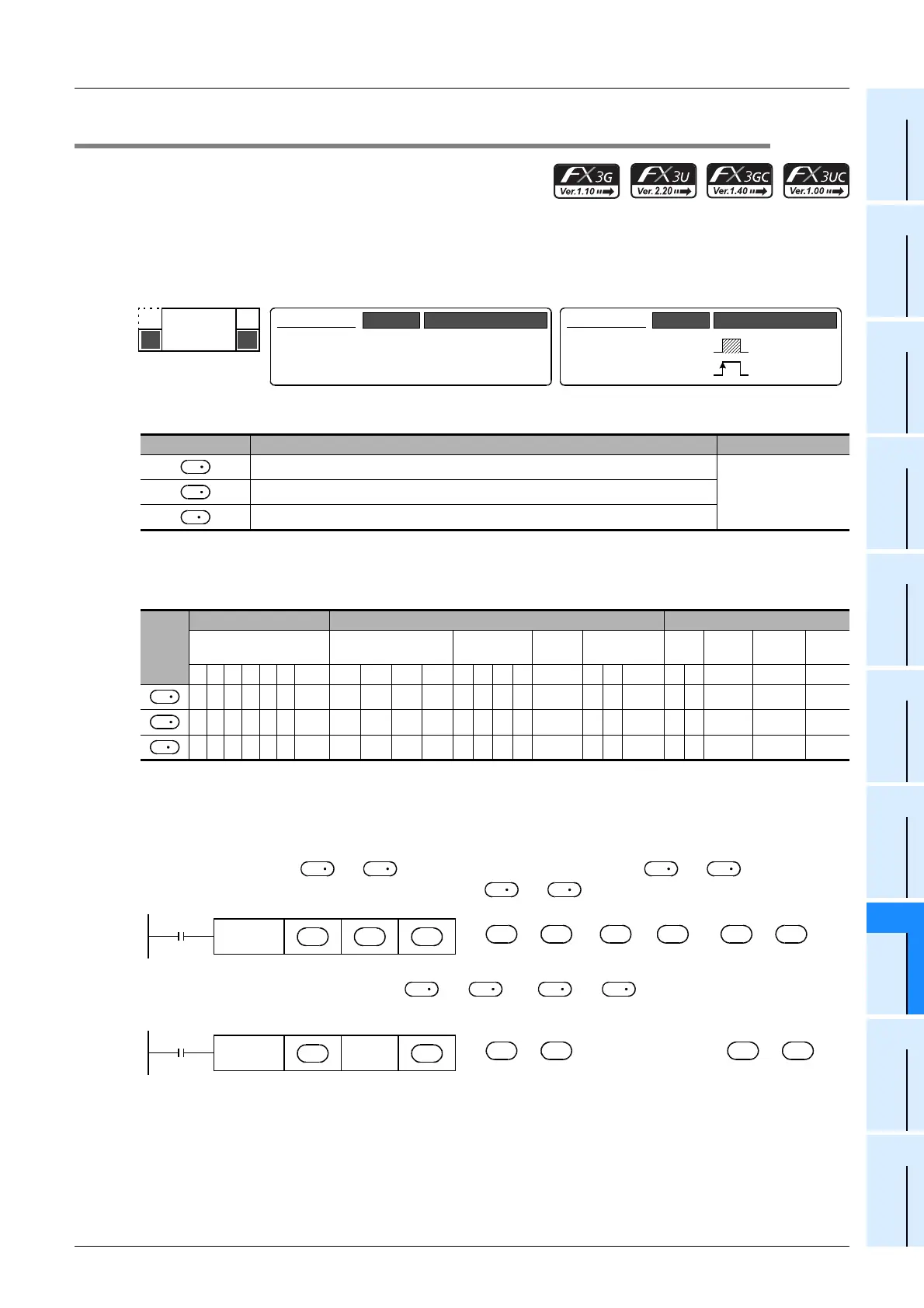

1. 32-bit operation (DEDIV and DESDIVP)

Binary floating point data [ +1, ] is divided by binary floating point data [ +1, ], and the division

result in the binary floating point format is transferred to [ +1, ].

When a constant (K or H) is specified as [ +1, ] or [ +1, ], it is automatically converted into

binary floating point.

Operand Type Description Data Type

Word device number storing binary floating point data used in division

Real number (binary)

*1

Word device number storing binary floating point data used in division

Data register number storing binary floating point data obtained by division

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD.b KnX KnY KnM KnS T C D R U\G VZModifyKH E ""P

33 S 333 3

33 S 333 3

33 S 3

P

FNC 123

EDIV

D

−

Mnemonic Operation Condition

16-bit Instruction

DEDIV

DEDIVP

Mnemonic Operation Condition

32-bit Instruction

13 steps

Continuous

Operation

Pulse (Single)

Operation

S

1

S

2

D

S

1

S

2

D

S

1

S

1

S

2

S

2

D

D

Command

input

FNC123

DEDIV

S

1

S

2

D

[ +1, ]

÷

[ +1, ]

→

[ +1, ]

Binary floating point Binary floating point Binary floating point

S

1

S

1

S

2

S

2

D

D

Dividend Divisor

S

1

S

1

S

2

S

2

Command

input

FNC123

DEDIV

K100

S

1

D

[ +1, ]

÷

[ K100 ]

→

[ +1, ]

Binary floating point Automatically

converted into binary

floating point

Binary floating point

S

1

S

1

D

D

Dividend Divisor

Loading...

Loading...