APPENDICES

APP − 56

MELSEC-A

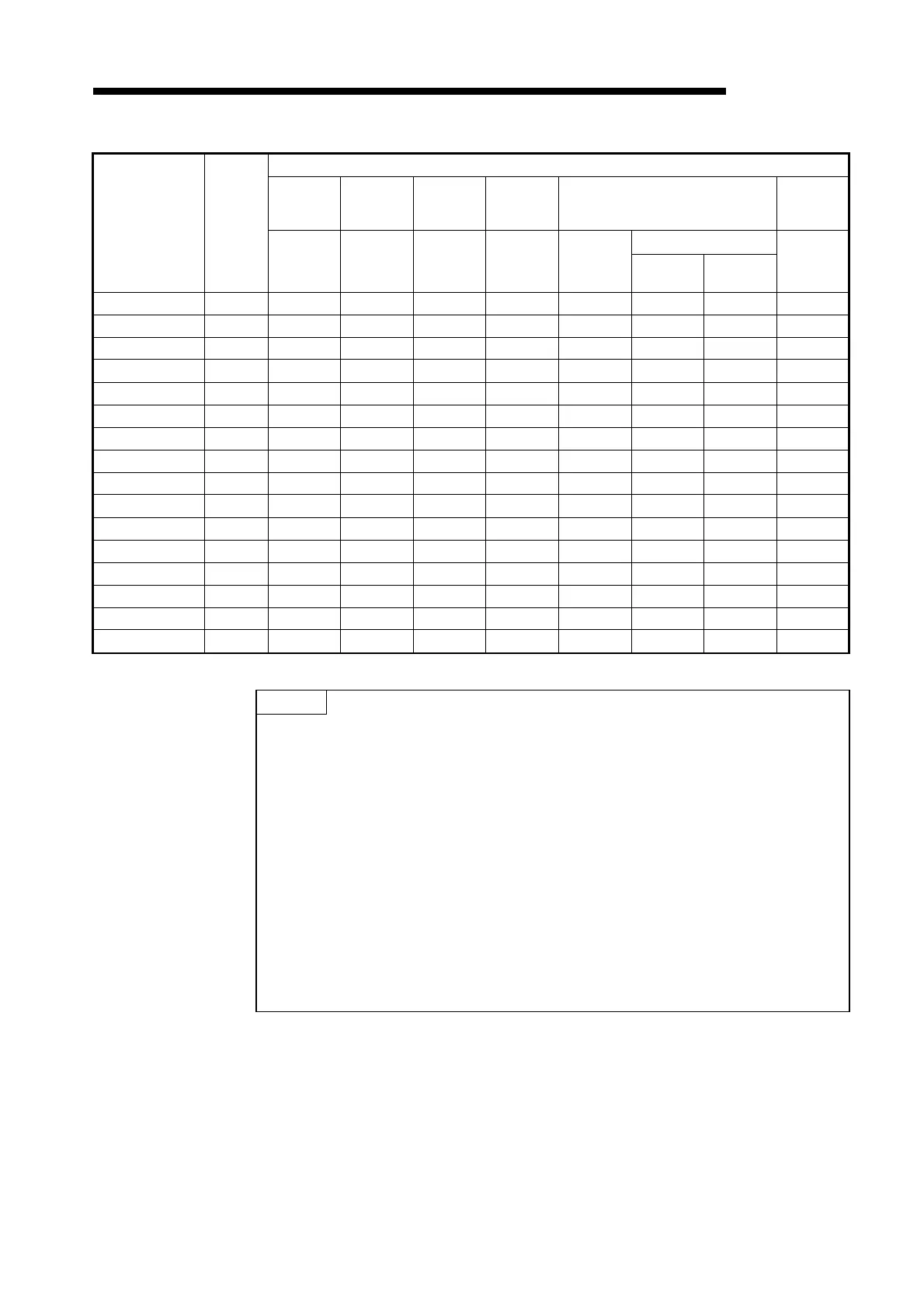

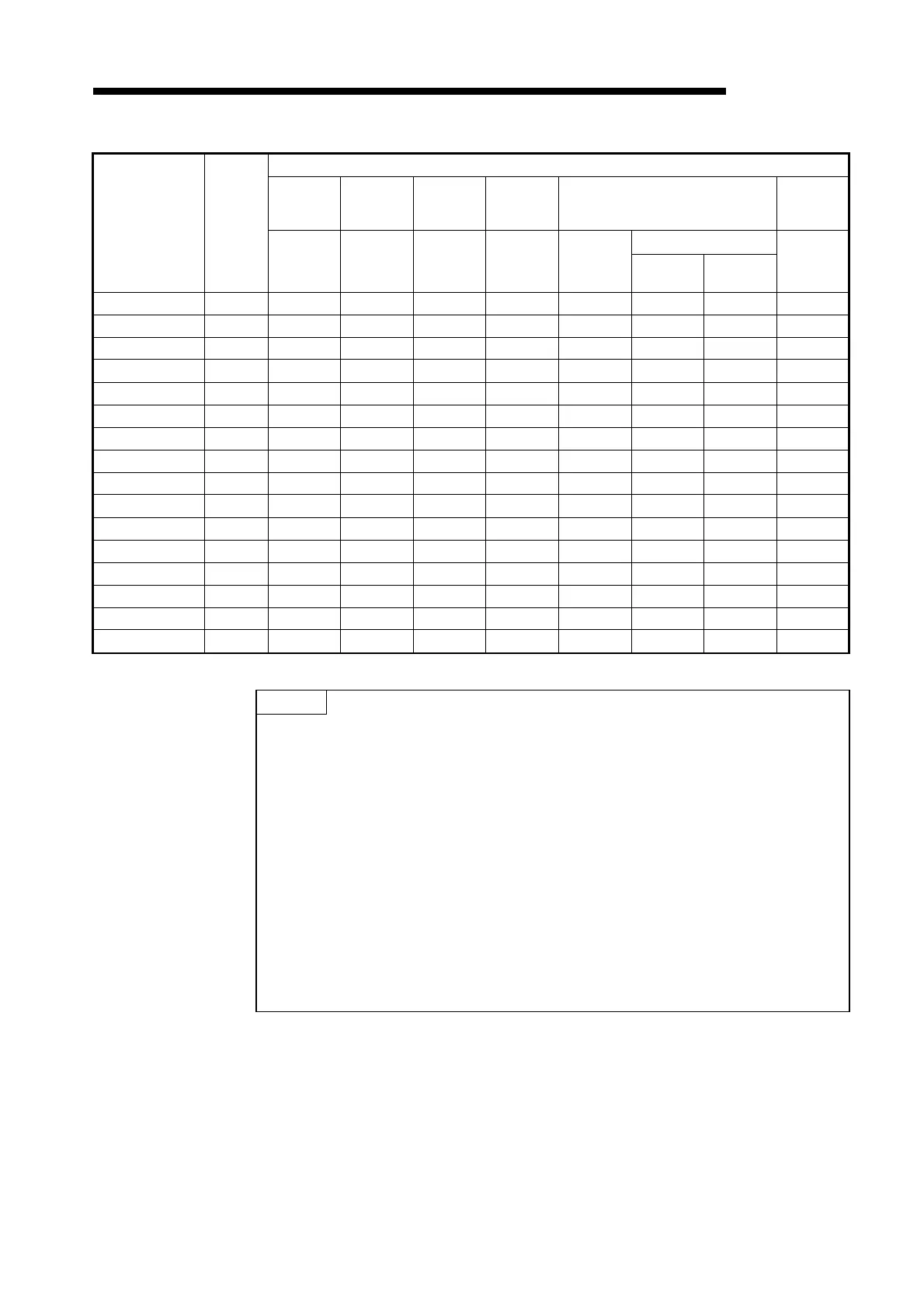

Table 2.2 Instruction Processing Time of Small Size, Compact CPUs (Continue)

Processing Time (µs)

A2AS (S1)

A2USH-S1

A2USH

board

A2C A52G A0J2H A1FX

Direct Mode

Instruction Condition

Refresh

Mode

Refresh

Mode

Refresh

Mode

Refresh

Mode

Refresh

Mode

Other

than X, Y

X, Y

Refresh

Mode

MOV 1.2 0.55 59 47 59 59 71 9.1

MOVP 1.2 0.55 59 47 59 59 71 8.9

DMOV 3.2 1.45 84 67 84 84 109 13.1

DMOVP 3.2 1.45 84 67 84 84 109 13.1

XCH 2.8 1.27 75 60 75 76 105 11.9

XCHP 2.8 1.27 75 60 75 76 105 11.9

DXCH 4.2 1.82 134 107 134 134 177 21.7

DXCHP 4.2 1.82 134 107 134 134 177 21.7

CML 2.4 1.09 54 43 54 54 72 8.3

CMLP 2.4 1.09 54 43 54 54 72 8.3

DCML 3.2 1.45 93 74 93 94 136 15.1

DCMLP 3.2 1.45 93 74 93 94 136 15.3

BMOV S D n n=96 72 32.73 499 399 499 501 8931 44.4

BMOVP S D n n=96 72 32.73 499 399 499 501 8931 44.5

FMOV S D n n=96 32 14.65 286 229 286 286 1287 25.4

FMOVP S D n n=96 32 14.65 286 229 286 286 1287 25.5

POINTS

(1) All the basic instructions indicated above are used without index

qualification.

(2) When unexecuted, any instruction is processed during the following time:

An, A2C and A0J2H............................... (Number of steps + 1) x 1.3 (µs)

AnN, AnS, A3V,A73 and A3N board ...... (Number of steps + 1) x 1.0 (µs)

A1SH, A1SJH......................................... (Number of steps + 1) x 0.33 (µs)

A2SH (S1), A1FX................................... (Number of steps + 1) x 0.25 (µs)

A3H and A3M......................................... (Number of steps + 1) x 0.2 (µs)

A2A, A2AS and A2U .............................. (Number of steps + 4) x 0.2 (µs)

A3A, A3U and A4U ................................ (Number of steps + 4) x 0.15 (µs)

A2USH-S1, A2USH board ..................... (Number of steps + 7) x 0.09 (µs)

Loading...

Loading...