APPENDICES

APP − 72

MELSEC-A

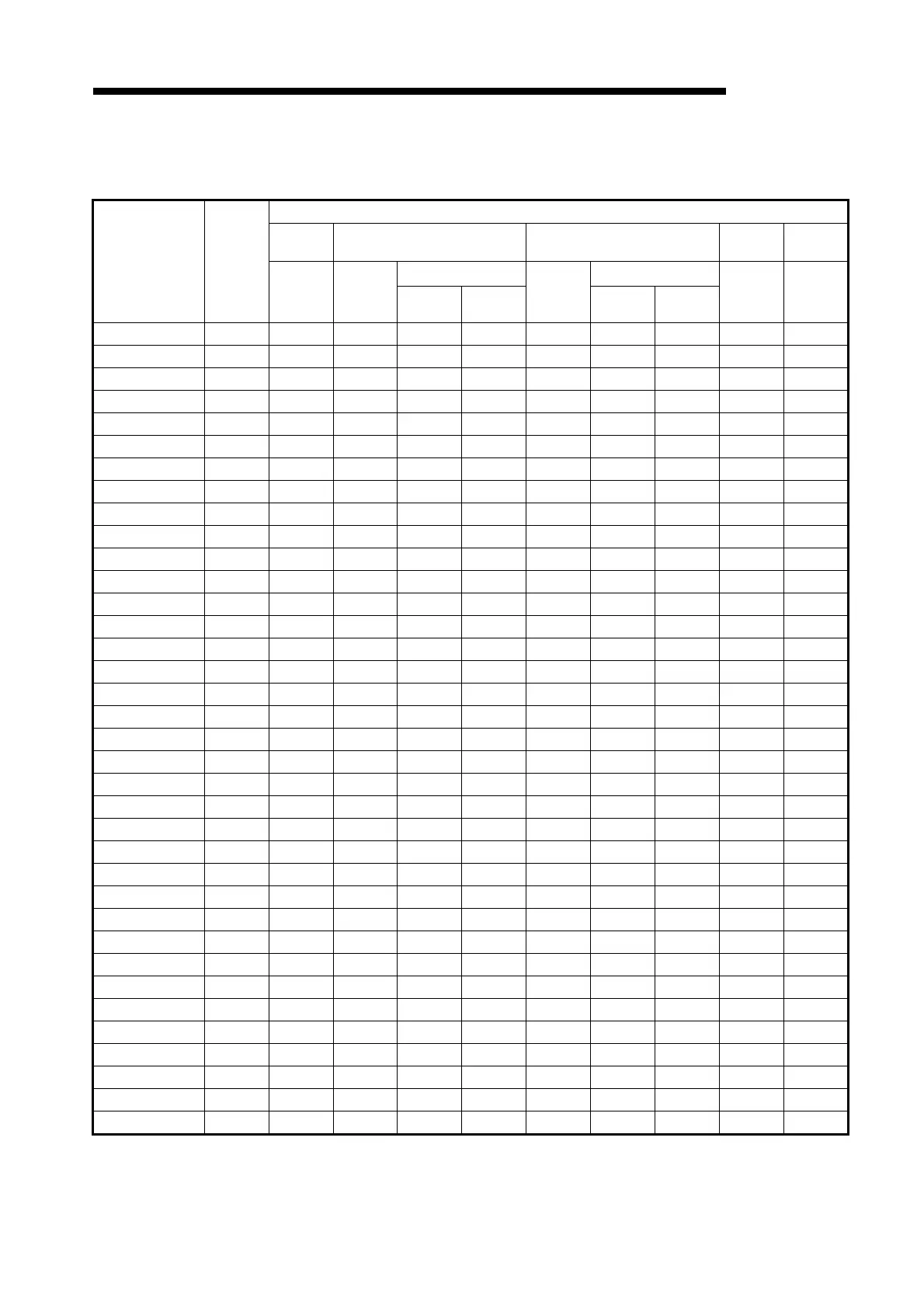

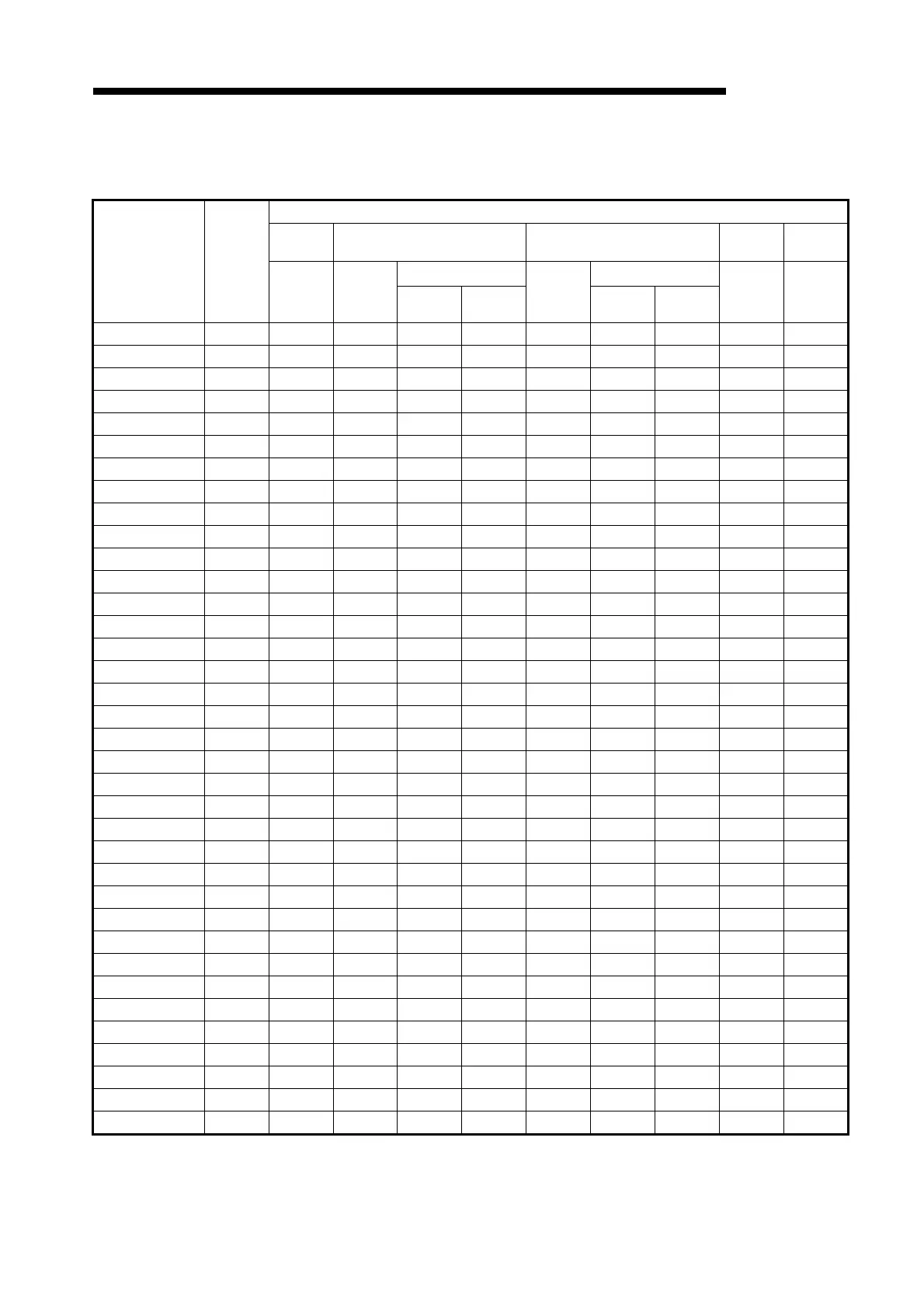

(2) Basic instruction

Table 2.5 Instruction Processing Time of CPUs

Processing Time (µs)

An

AnN, A3V, A73

A3N board

A3H, A3M A2A, A2U

A3A,

A3U, A4U

D D

Instruction Condition

D R

Other

than X, Y

X, Y

R

Other

than X, Y

X, Y

R R

LD= 95 70 70 87 2.8 2.8 10 3.8 2.9

AND= 96 61 62 81 1.8 1.8 9.4 2.6 2.0

OR= 94 67 66 85 3.2 3.2 11 2.8 2.1

LDD= 238 133 134 119 157* 157* 180* 10 7.7

ANDD= 231 124 125 210 157* 157* 180* 5.9 4.4

ORD= 236 133 133 218 158* 158* 181* 6.3 4.7

LD<> 98 69 69 86 2.8 2.8 10 4.1 3.1

AND<> 92 60 60 79 1.8 1.8 9.4 2.6 2.0

OR<> 96 66 66 84 3.2 3.2 11 2.8 2.1

LDD<> 235 131 132 217 158* 158* 181* 10 7.7

ANDD<> 239 129 129 215 158* 158* 181* 5.9 4.4

ORD<> 234 129 129 214 161* 161* 184* 6.1 4.6

LD> 96 67 67 84 2.8 2.8 10 4.1 3.1

AND> 92 60 60 79 1.8 1.8 9.4 2.6 2.0

OR> 98 66 65 83 3.2 3.2 11 2.8 2.1

LDD> 238 133 133 219 158* 158* 181* 9.7 7.3

ANDD> 240 131 131 217 158* 158* 181* 5.8 4.4

ORD> 236 131 130 219 161* 161* 184* 6.0 4.5

LD>= 100 71 71 88 2.8 2.8 10 4.1 3.1

AND>= 94 61 61 81 1.8 1.8 9.4 2.6 2.0

OR>= 100 69 68 86 3.2 3.2 11 2.8 2.1

LDD>= 243 137 137 222 160* 158* 181* 9.7 7.3

ANDD>= 238 127 128 213 158* 158* 181* 5.8 4.4

ORD>= 246 137 136 221 161* 161* 183* 6.0 4.5

LD< 96 69 69 86 2.8 2.8 10 4.1 3.1

AND< 92 59 60 79 1.8 1.8 9.4 2.6 2.0

OR< 96 66 65 84 3.2 3.2 11 2.8 2.1

LDD< 238 133 133 219 159 159 182 9.7 7.3

ANDD< 241 131 131 217 158 158 181 5.8 4.4

ORD< 236 131 130 215 160 160 183 6.0 4.5

LD<= 100 71 71 88 2.8 2.8 10 4.1 3.1

AND<= 94 61 61 80 1.8 1.8 9.4 2.6 2.0

OR<= 100 69 68 86 3.2 3.2 11 2.8 2.1

LDD<= 244 137 136 222 158* 160* 181* 9.7 7.3

ANDD<= 238 127 128 213 158* 158* 181* 5.8 4.4

ORD<= 246 137 136 221 161* 161* 184* 6.0 4.5

R: Refresh mode, D: Direct mode

* With an A3M, processing time will be 20 µs longer than the indicated time.

Loading...

Loading...