3. INSTRUCTION STRUCTURE

3 − 9

MELSEC-A

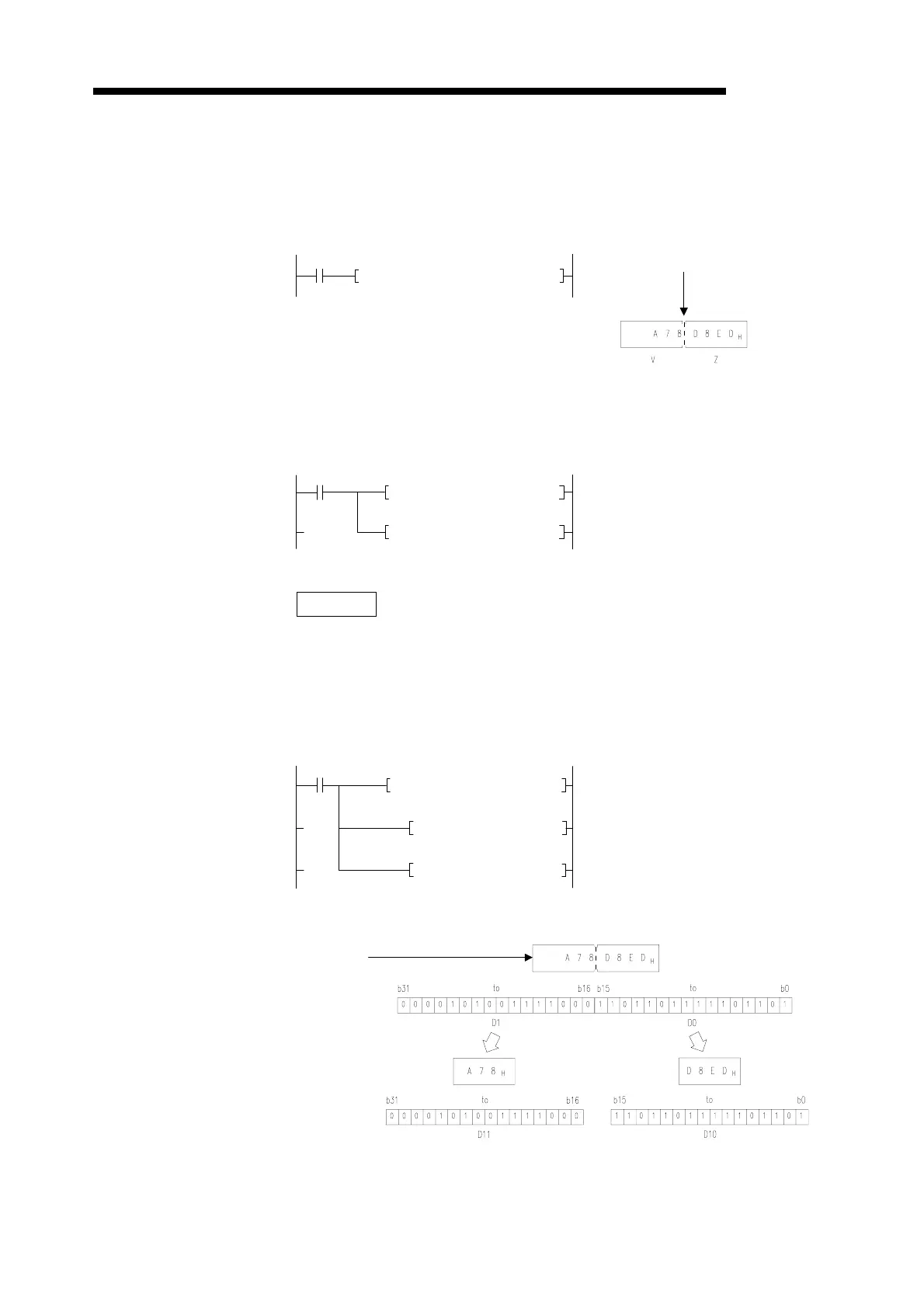

2) Index registers can process 32-bit instructions when Z and V are used

in pairs. In this case, Z is regarded as the lower 16-bit device, and

therefore, V cannot be used in a 32-bit instruction. (Programs cannot be

entered.)

If either of Z or V is specified for index qualification in the instruction,

index qualification is performed regarding data in Z and V as 16-bit data

even when 32-bit data is stored in Z and V.

REMARK

To handle 32-bit data with extension index registers Z1 to Z6 and V1 to V6 of AnA, A2AS, AnU,

QCPU-A (A Mode) and A2USH board, refer to Section 3.8.5.

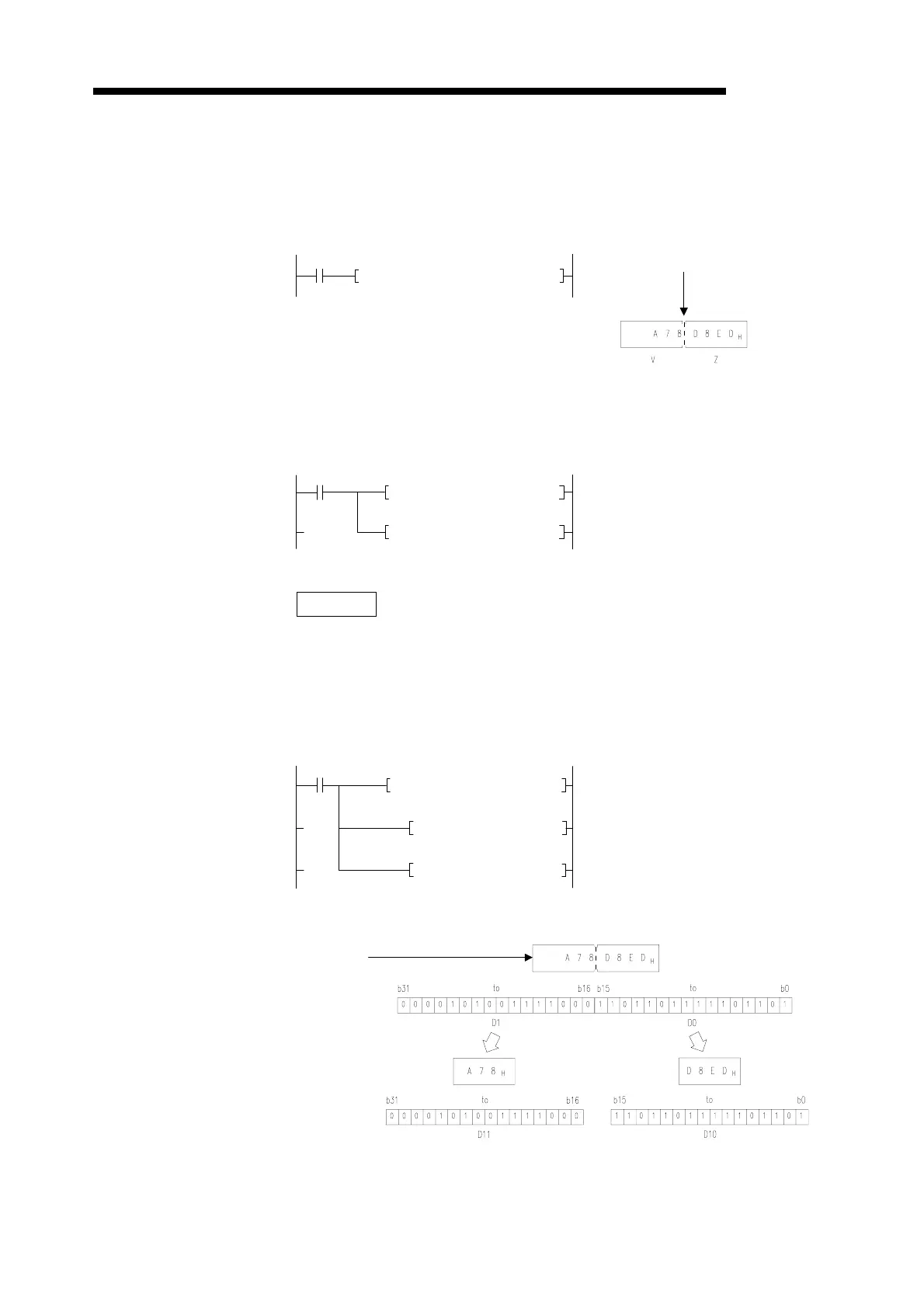

3) If one of two consecutive word devices used to store 32-bit data is used

in a 16-bit instruction, processing goes as follows.

X010

DMOV

H

0A78D8ED

Z

HA78D8ED

X10 ON

X010

DMOV

H

12345678

Z

DMOV

D2

D0

Z

Data 12345678H is stored in Z and V.

⋅⋅⋅⋅⋅⋅ Data in D0 and D1 become equal to

D(2+5678H) and D(3+5678H), respectively.

X010

DMOV

H

0A78D8ED

D0

MOV

MOV

D0

D1

D10

D11

When D0 is specified:

Data b0 to b15 of D0 and D1 are

handled as D0 data.

When D1 is specified:

Data b16 to b31 of D0 and D1

are handled as D1 data.

HA78D8ED

X10 ON

Loading...

Loading...