5. SEQUENCE INSTRUCTIONS

5 − 8

MELSEC-A

ORB

When circuit blocks are parallelly connected consecutively, the coding of program is

available in two types. However, proceed with the coding according to Coding

example 1.

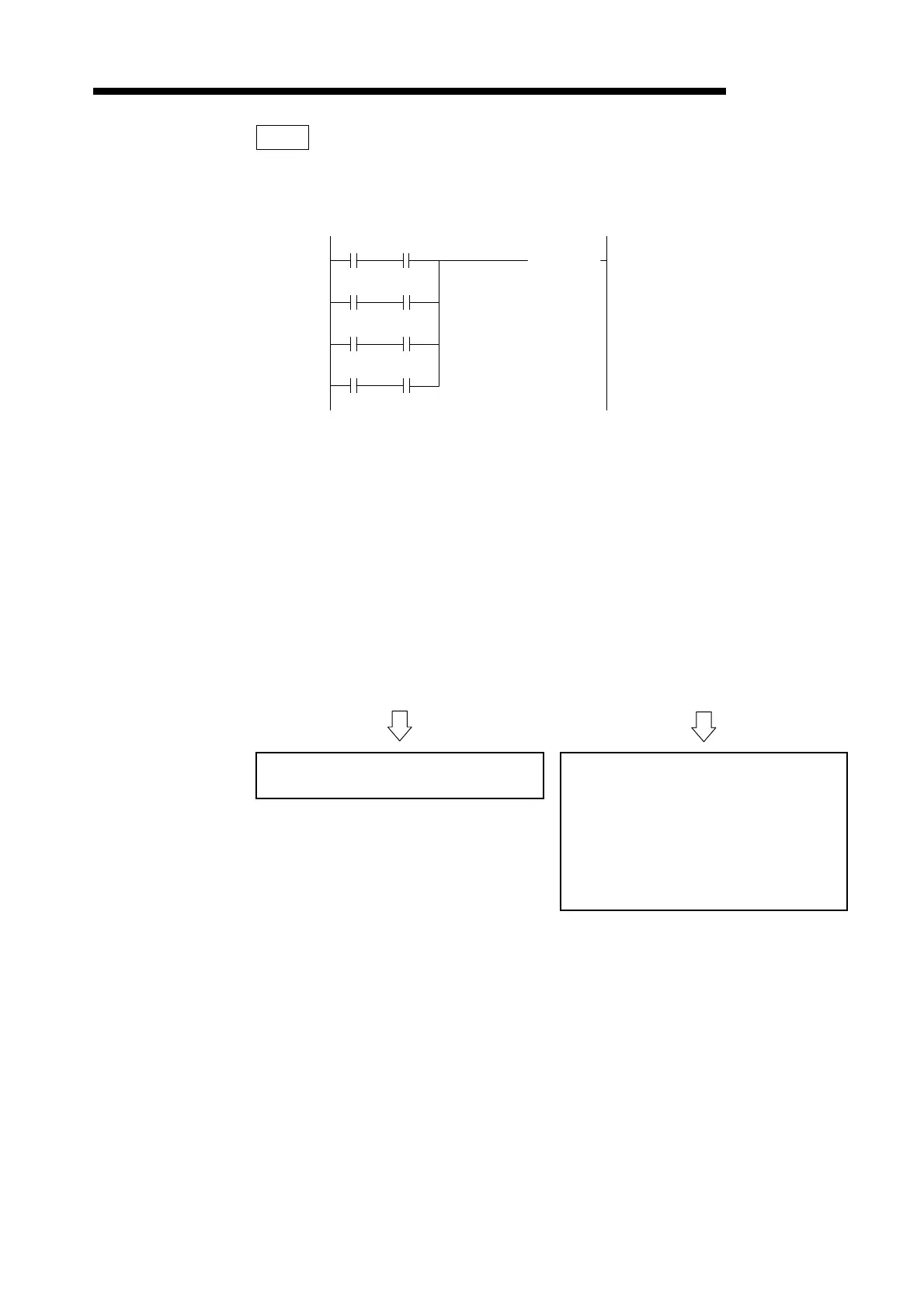

()

X001 X000

X003 X002

M7

0

X005 X004

X007 X006

• Coding example 1

0 LD X000

1 AND X001

2 LD X002

3 AND X003

4 ORB

5 LD X004

6 AND X005

7 ORB

8 LD X006

9 AND X007

10 ORB

11 OUT M7

12 END

• Coding example 2

0 LD X000

1 AND X001

2 LD X002

3 AND X003

4 LD X004

5 AND X005

6 LD X006

7 AND X007

8 ORB

9 ORB

10 ORB

11 OUT M7

12 END

There is restriction on the number of ORBs

used.

If ORBs are written consecutively exceeding the

number mentioned below, the PC canno

per-form proper operation.

For AnA, A2AS, AnU, QCPU-A (A Mode) and

A2USH board: 15 instructions

(16 blocks)

For CPUs other than AnA, A2AS,AnU, QCPU-

(A Mode) and A2USH board: 7 instructions

(8 blocks)

Loading...

Loading...