3-6 Theory of Operation: Transceiver Board

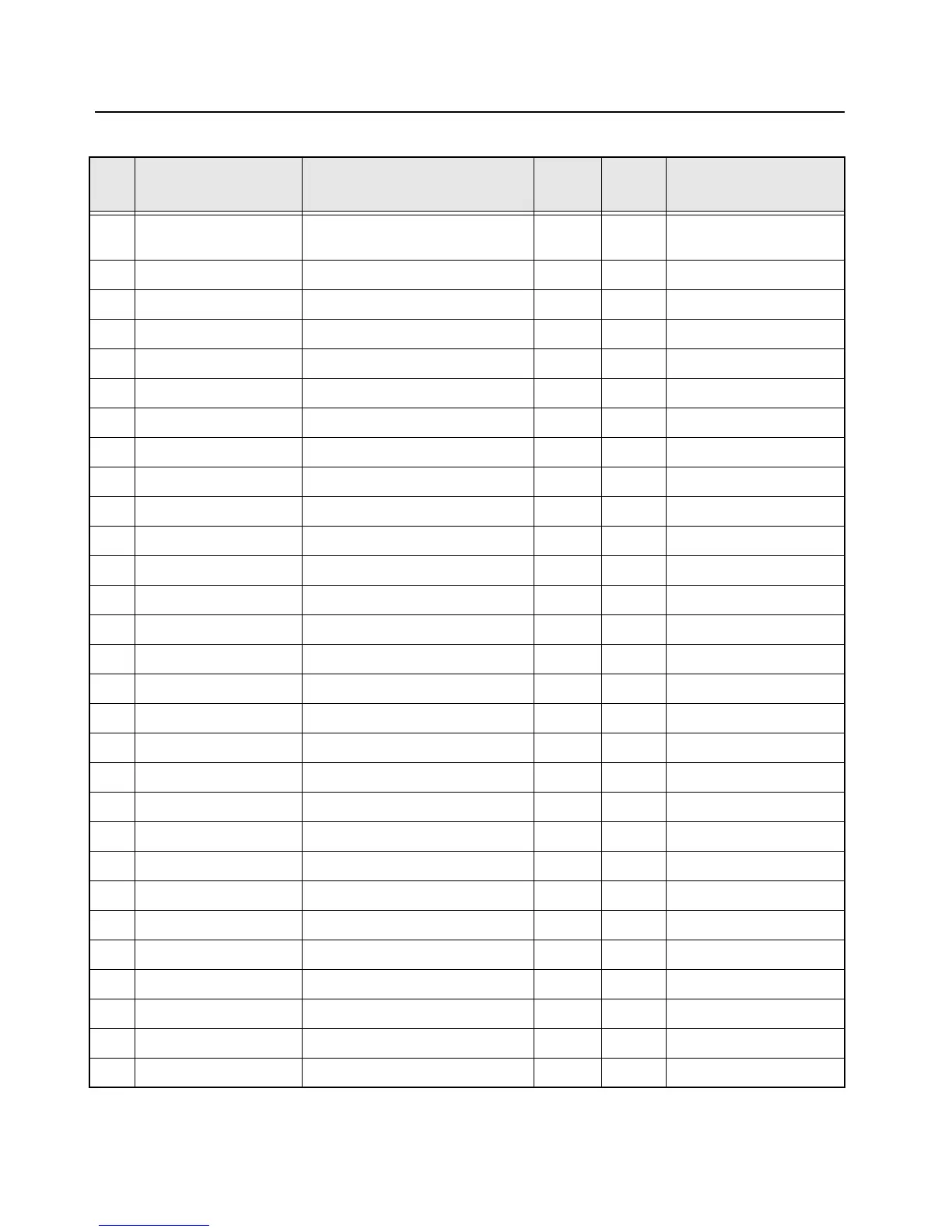

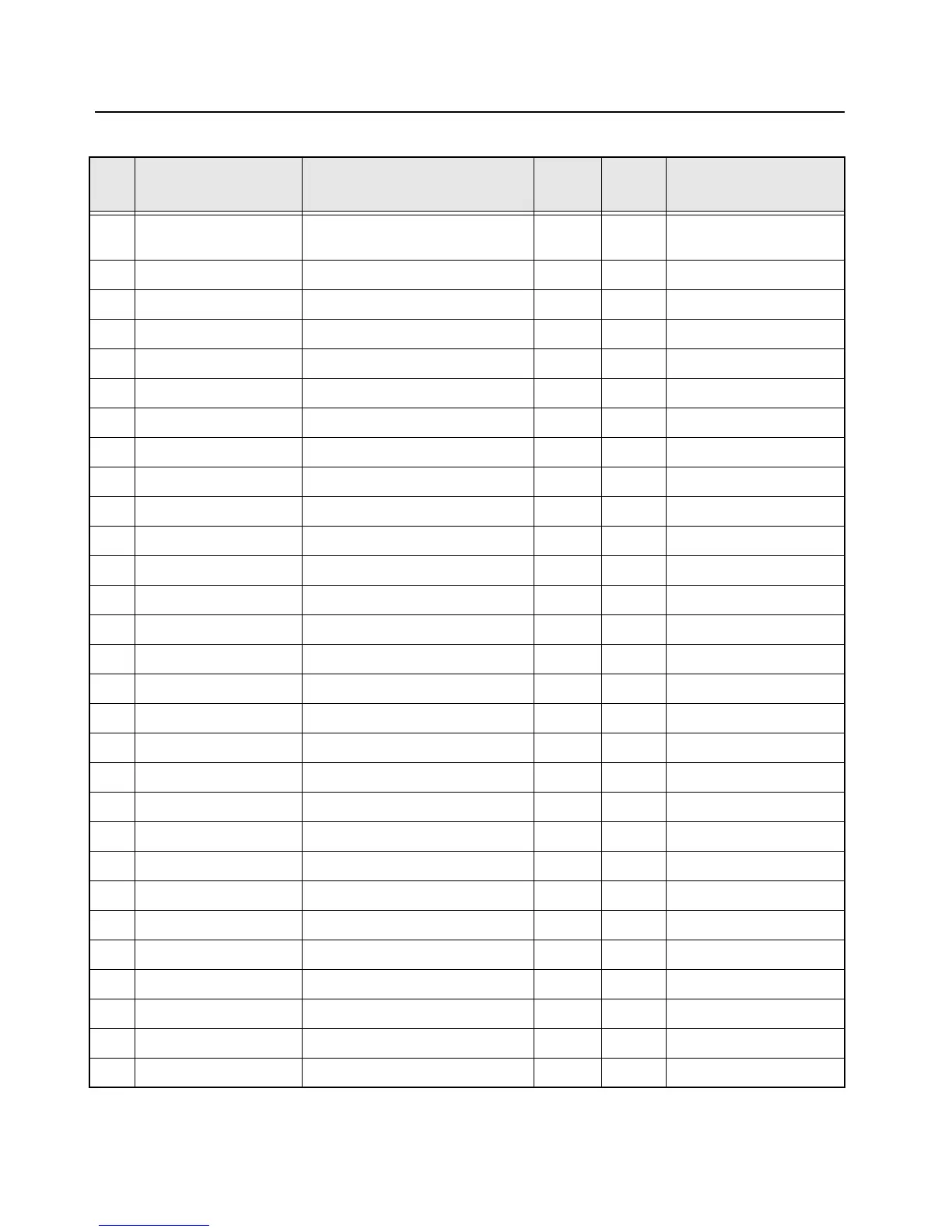

12 TX_INH DIG_CTRL_TX_INHIBIT_TYPE_1 I control TX inhibit control for

secure

13 RX_DA DIG _DATA _SSI _RX _DOUTA O ssi RX SSI data

14 RF_DAC_SPI_CS DIG_CTRL_SPI_DAC_PE I spi SPI DAC chip select

15 RX_CLK CLK_SSI_RX O ssi RX SSI clock

16 ISET ANA_CTRL_ISET I control MAKO Ramp

17 TX_FSYNC DIG_TX_SSI_FS I ssi TX SSI frame sync

18 TX_DA_CONN DIG_DATA_TX_SSI I ssi TX SSI data

19 TX_CLK DIG_TX_SSI_CLK I ssi TX SSI clock

20 V_Coin_Cell V_Coin_Cell – dc Coin cell battery

21 GPS_ANT RF_GPS O rf GPS_RF signal

22 ABACUS_SPI_CS DIG_CTRL_SPI_ABACUS_PE I spi SPI Abacus chip select

23 F2_SYNCB DIG_SYNCB I control Synchronize RX SSI data

24 GROUND GROUND – – –

25 LOCK_DET_A DIG_CTRL_LOCK O status FGU lock detect

26 BSTAT DIG_BATTERY_DATA I/O 1 wire IMPRES Battery status

27 TRIDENT_SPI_CS DIG_CTRL_SPI_TRIDENT_PE I spi SPI Trident chip select

28 UNSW_B+ DC_FUSED _B+ O dc Fused B+ to VOCON

29 SPI_DSP_MISO DIG_DATA_SPI_MISO O spi SPI data out

30 UNSW_B+ DC_FUSED _B+ O dc Fused B+ to VOCON

31 SPI_DSP_MOSI DIG_DATA_SPI_MOSI I/O spi SPI data I/O

32 UNSW_B+ DC_FUSED _B+ O dc Fused B+ to VOCON

33 SPI_DSP_CLK DIG_SPI_CLK I spi SPI clock

34 UNSW_B+ DC_FUSED _B+ O dc Fused B+ to VOCON

35 GROUND GROUND – – –

36 UNSW_B+ DC_FUSED _B+ O dc Fused B+ to VOCON

37 VCC_SW_3.6 DC_SW1_3_6V I dc Regulated 3.6 V

38 GROUND GROUND – – –

39 GROUND GROUND – – –

40 GROUND GROUND – – –

Table 3-2. VOCON Connector J1001 (Continued)

Pin

No.

VOCON Signal XCVR Signal

XCVR

I/O

Type Description

Loading...

Loading...