NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 67

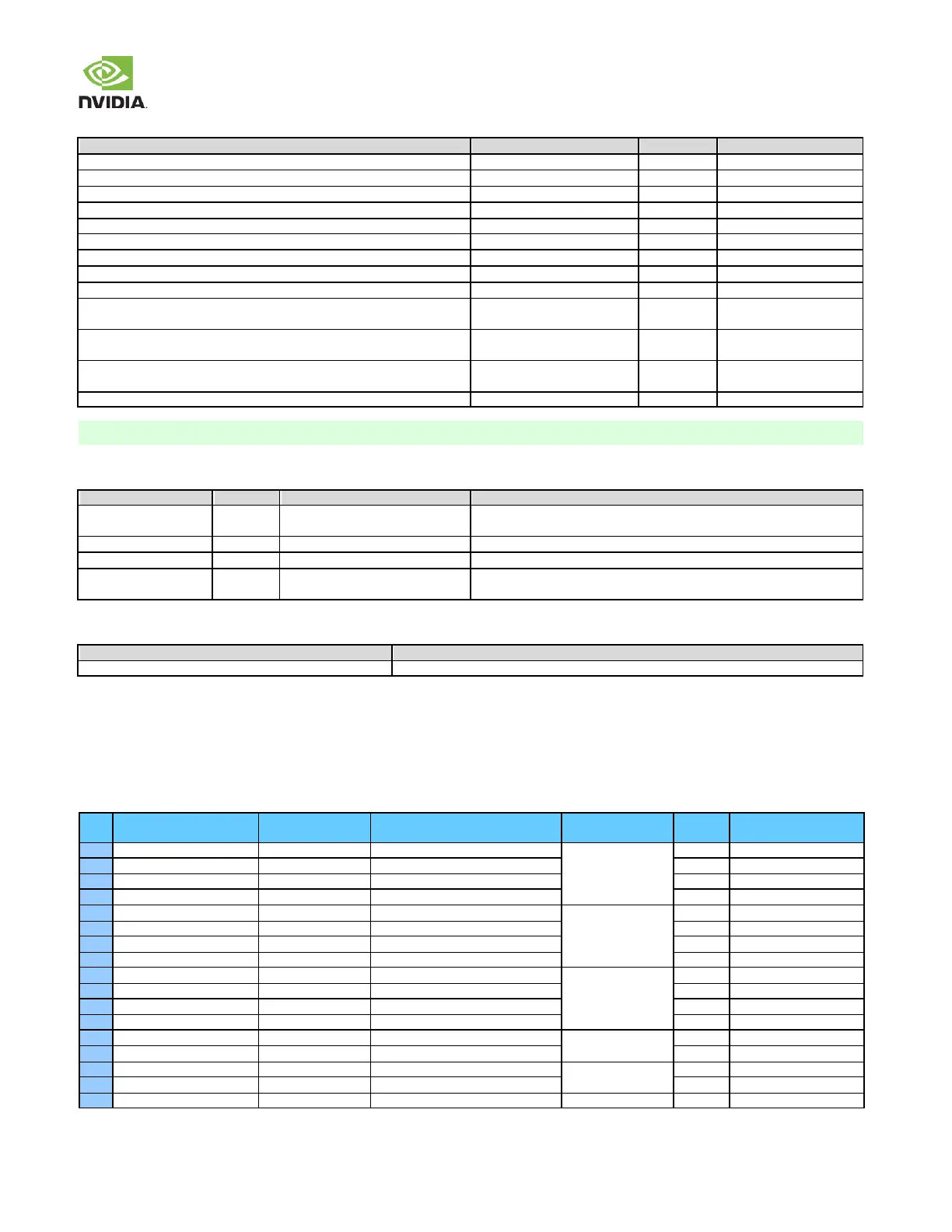

Table 72. SPI Interface Signal Routing Requirements

Configuration / Device Organization

Max Loading (total of all loads)

Breakout Region Impedance

Via proximity (Signal to reference)

Trace spacing Microstrip / Stripline

Max Trace Length/Delay (PCB Main Trunk) Point-Point

For MOSI, MISO, SCK & CS 2x-Load Star/Daisy

Max Trace Length/Delay (Branch-A) 2x-Load Star/Daisy

for MOSI, MISO, SCK & CS

Max Trace Length/Delay (Branch-B) 2x-Load Star/Daisy

for MOSI, MISO, SCK & CS

Max Trace Length/Delay Skew from MOSI, MISO & CS to SCK

Up to 4 signal Vias can share a single GND return Via

Table 73. SPI Signal Connections

SPI0_CLK has 120

(on the module).

SPI Clock.: Connect to Peripheral CLK pin(s)

SPI Data Output: Connect to Slave Peripheral MOSI pin(s)

SPI Data Input: Connect to Slave Peripheral MISO pin(s)

SPI2_CS[1:0]#

SPI[1:0]_CS0#

SPI Chip Selects.: Connect one CS_N pin per SPI IF to each Slave

Peripheral CS pin on the interface

Table 74. Recommended SPI observation (test) points for initial boards

One for each SPI signal line used

Near the module & Device pins.

12.3 UART

Jetson TX2/TX2i brings five UARTs out to the main connector. One of the UARTs is used for the WLAN/BT on Jetson TX2 or

as UART3 at the connector depending on the setting of a multiplexor. See Table 76 for typical assignments of the UARTs.

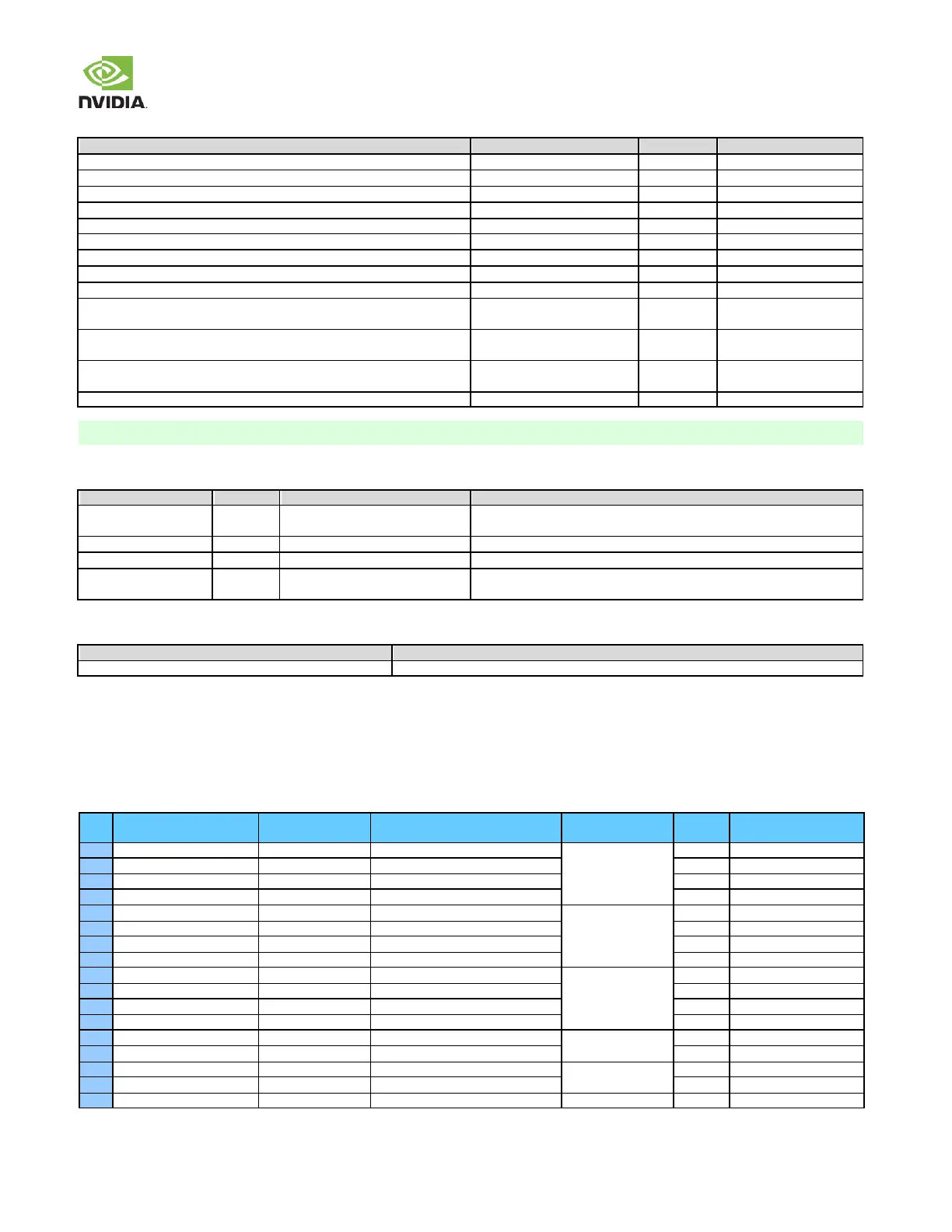

Table 75. UART Pin Descriptions

Usage on the Carrier

Board

UART 3 Clear to Send (muxed on TX2)

UART 3 Request to Send (muxed on TX2)

UART 3 Receive (muxed on TX2)

Optional source of

UART on Exp. Header

UART 3 Transmit (muxed on TX2)

Loading...

Loading...