NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 76

▪ Buffers or level shifters can be used to separate the signals from devices that may be affected. The buffer/shifter

should be disabled until the device power is enabled.

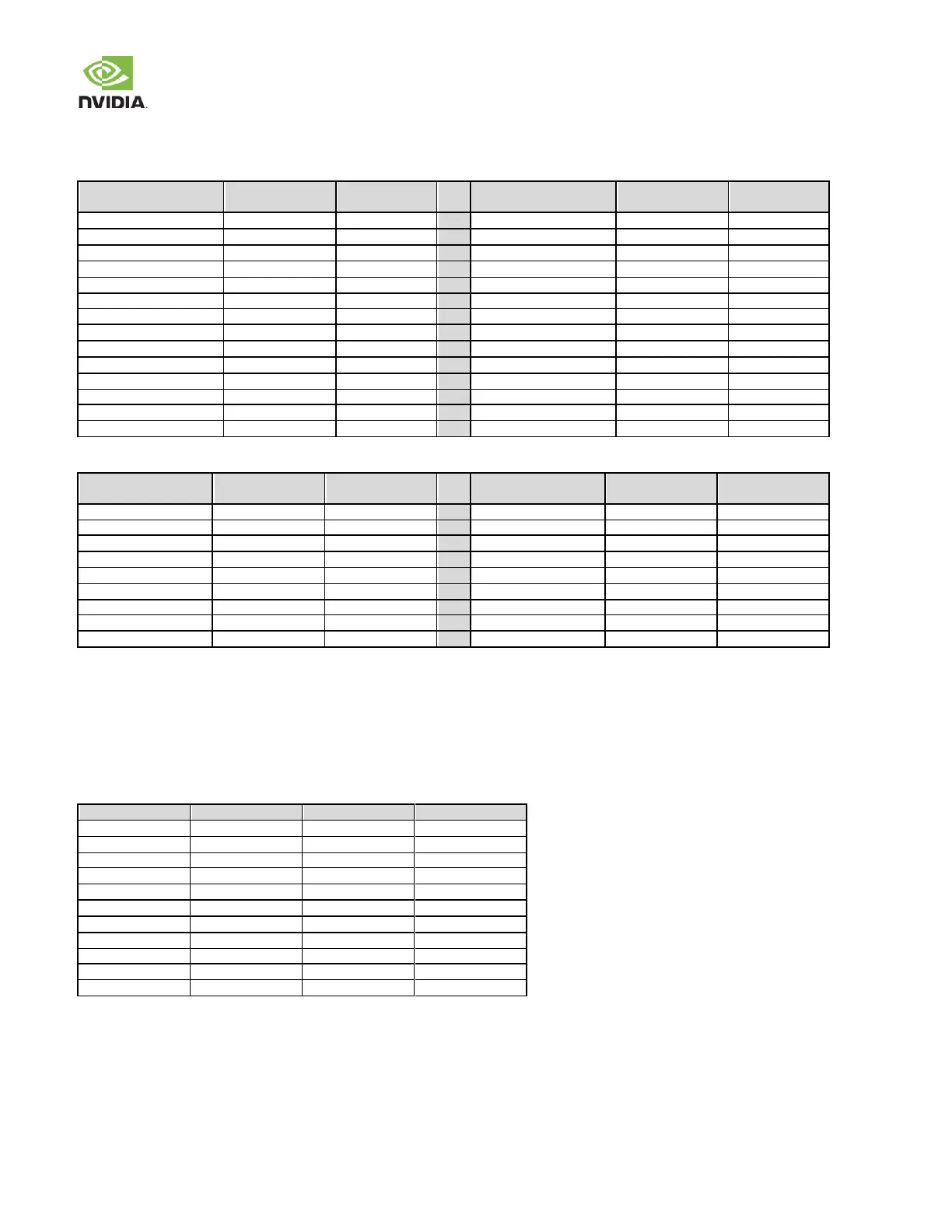

Table 87. Module Pins Pulled/Driven High by Tegra Prior to CARRIER_PWR_ON Active

Table 88. Module Pins Pulled High on the Module Prior to CARRIER_PWR_ON Active

Pull-up Supply

Voltage (V)

Pull-up Supply

Voltage (V)

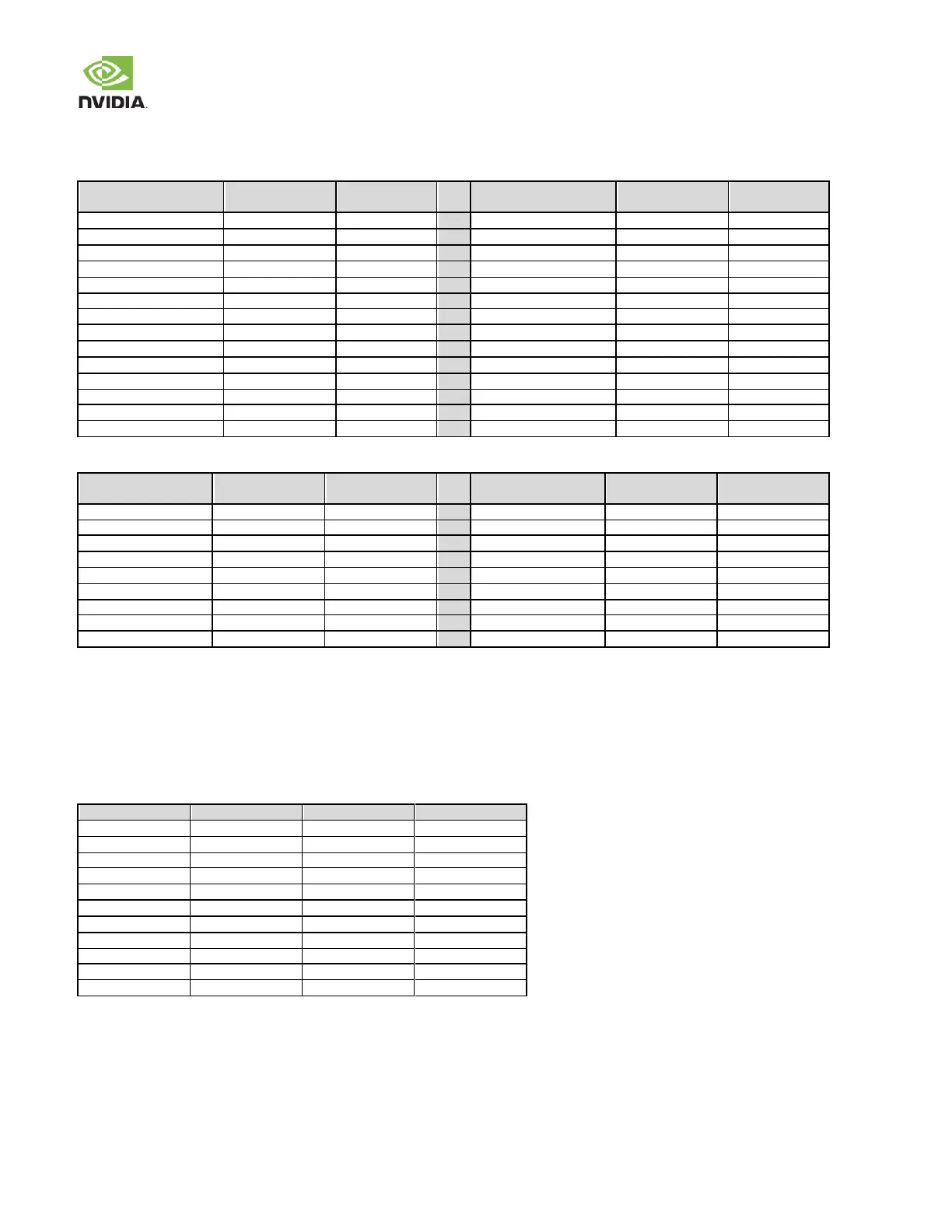

13.5 Pad Drive Strength

The table below provides the maximum MPIO pad output drive current w hen the pad is configured for the maximum

DRVUP/DRVDN values (11111b). The MPIO pad types include the ST, DD, CZ and LV_CZ type pads. The pad types can be

found in the Jetson TX2/TX2i Module Data Sheet.

Table 89. MPIO Maximum Output Drive Current

Loading...

Loading...