NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 51

8.0 MIPI CSI (VIDEO INPUT)

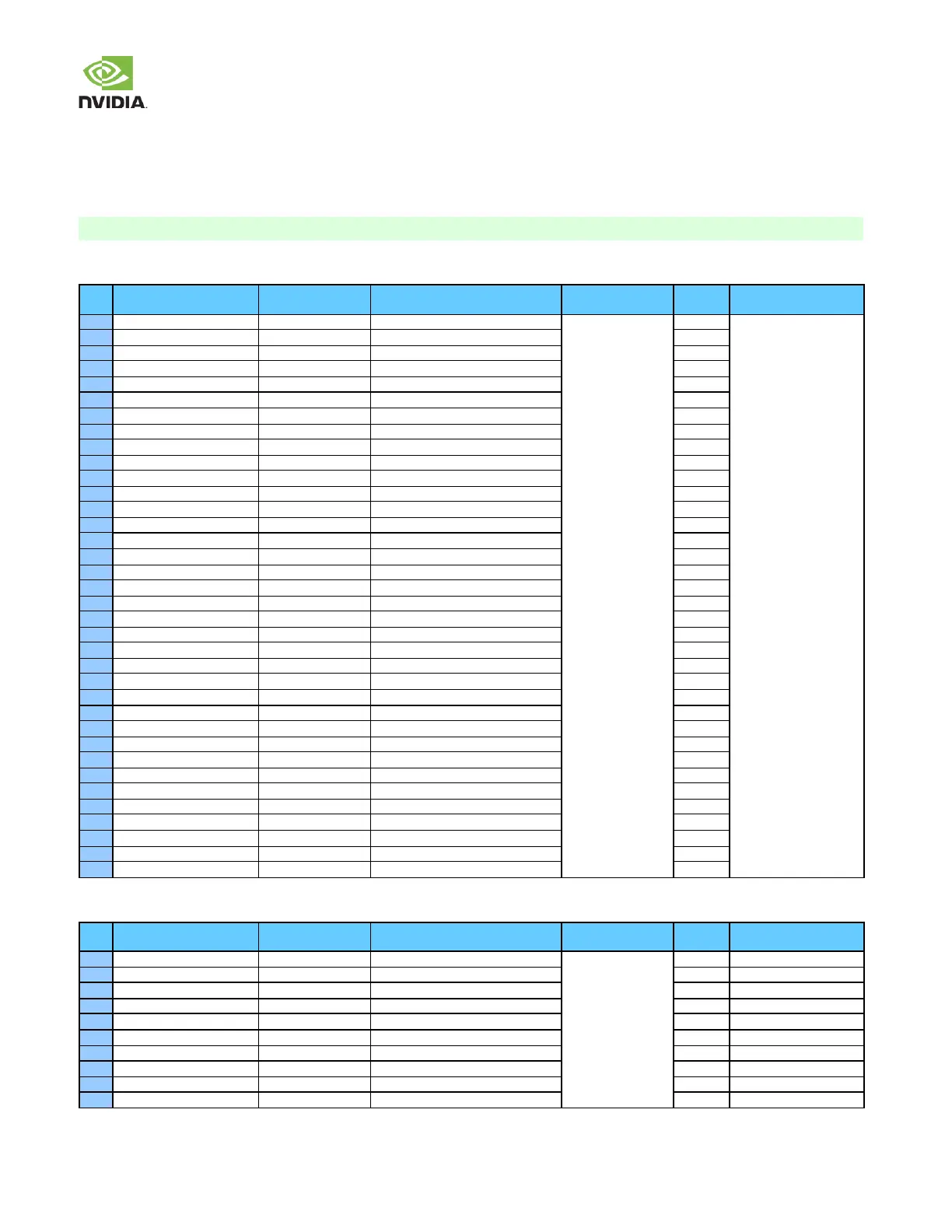

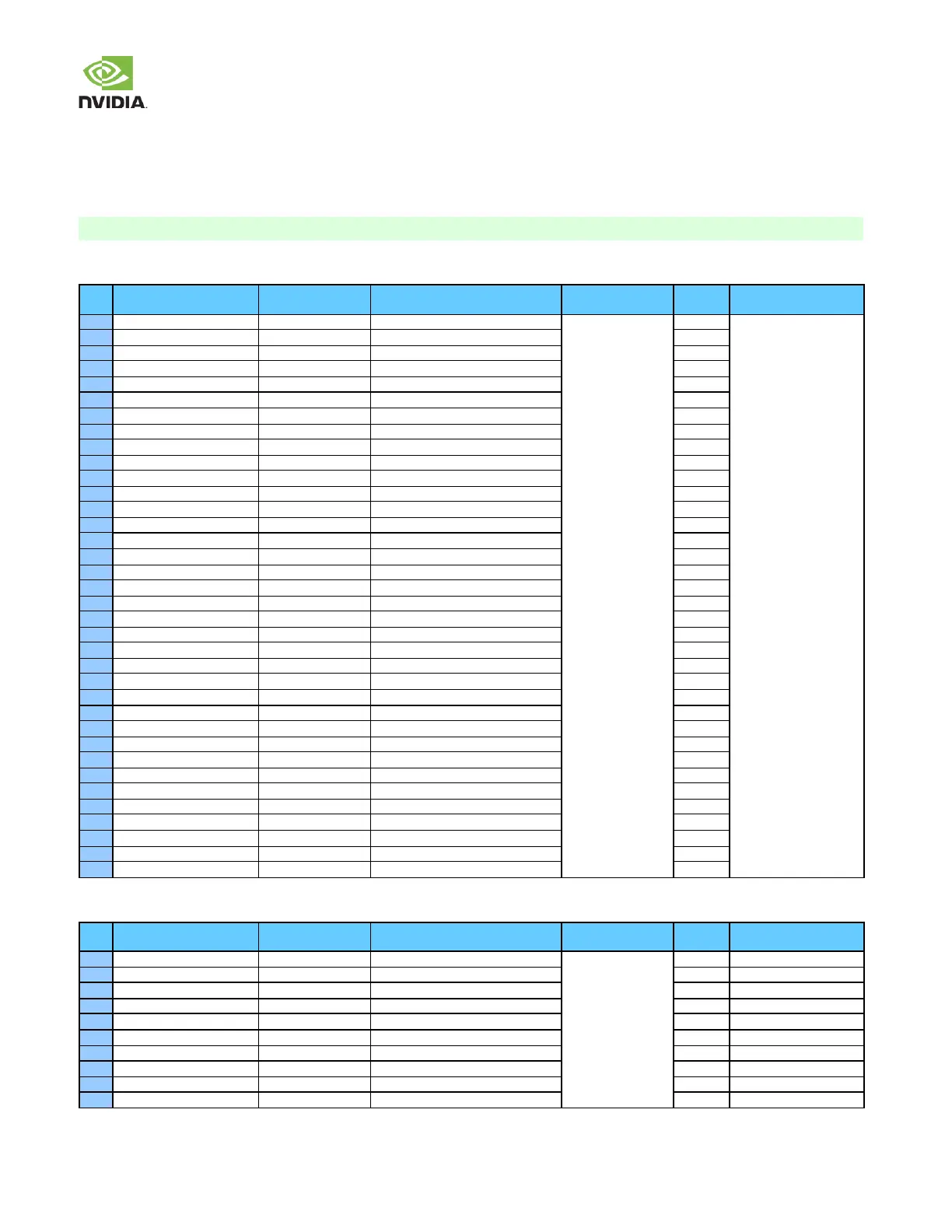

Jetson TX2/TX2i supports three MIPI CSI x4 bricks, allow ing a variety of device types and combinations to be supported. Up to

three quad lane cameras or six dual lane cameras are possible (see CSI Configurations table for details). Each data lane has a

peak bandw idth of up to 2.5Gbps.

Loading...

Loading...