NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 23

5.0 USB, PCIE & SATA

Jetson TX2/TX2i allow s multiple USB 3.0 & PCIe interfaces, and a single SATA interface to be brought out on the module. In

some cases, these interfaces are multiplexed on some of the module pins.

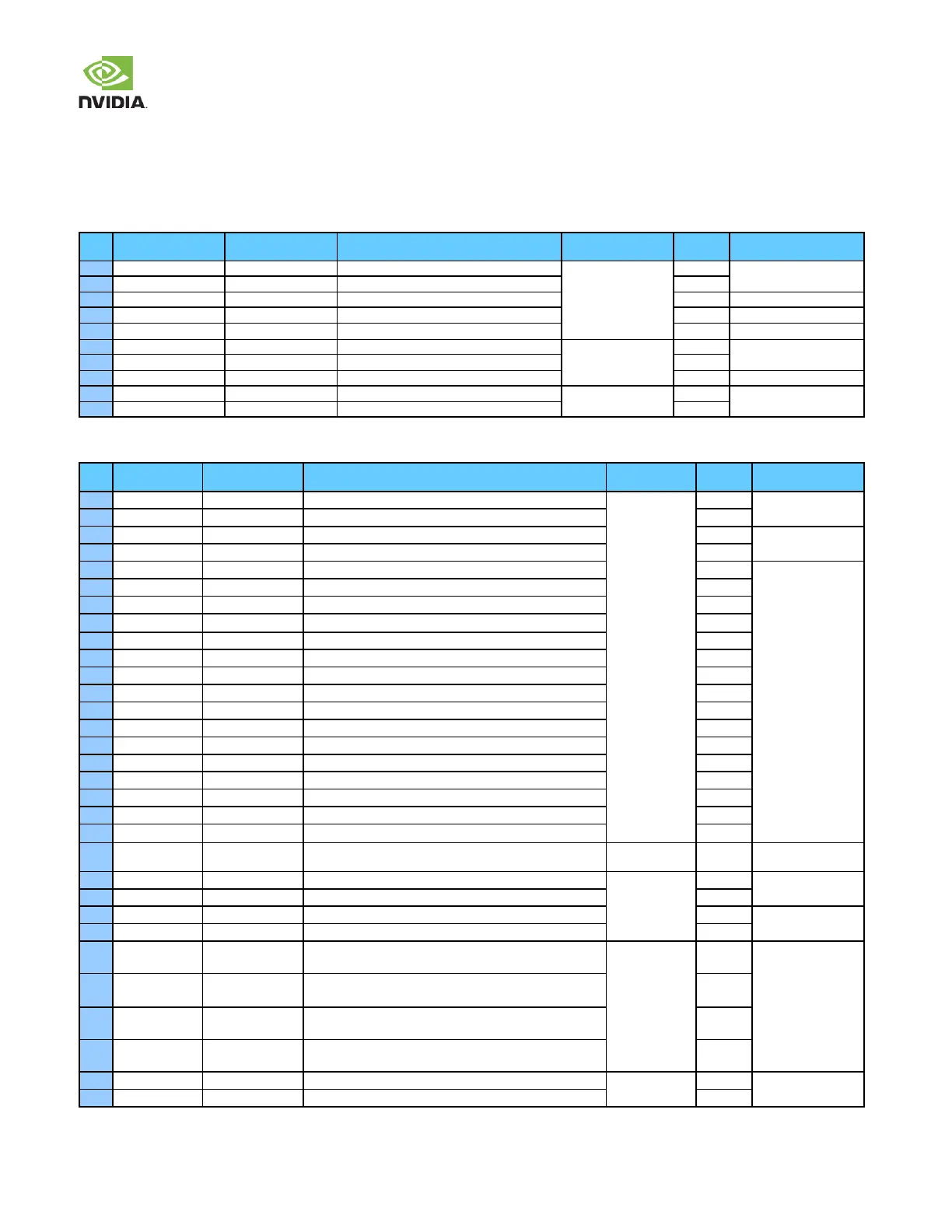

Table 13. USB 2.0 Pin Descriptions

USB VBUS Enable/Overcurrent 0

USB VBUS Enable/Overcurrent 1

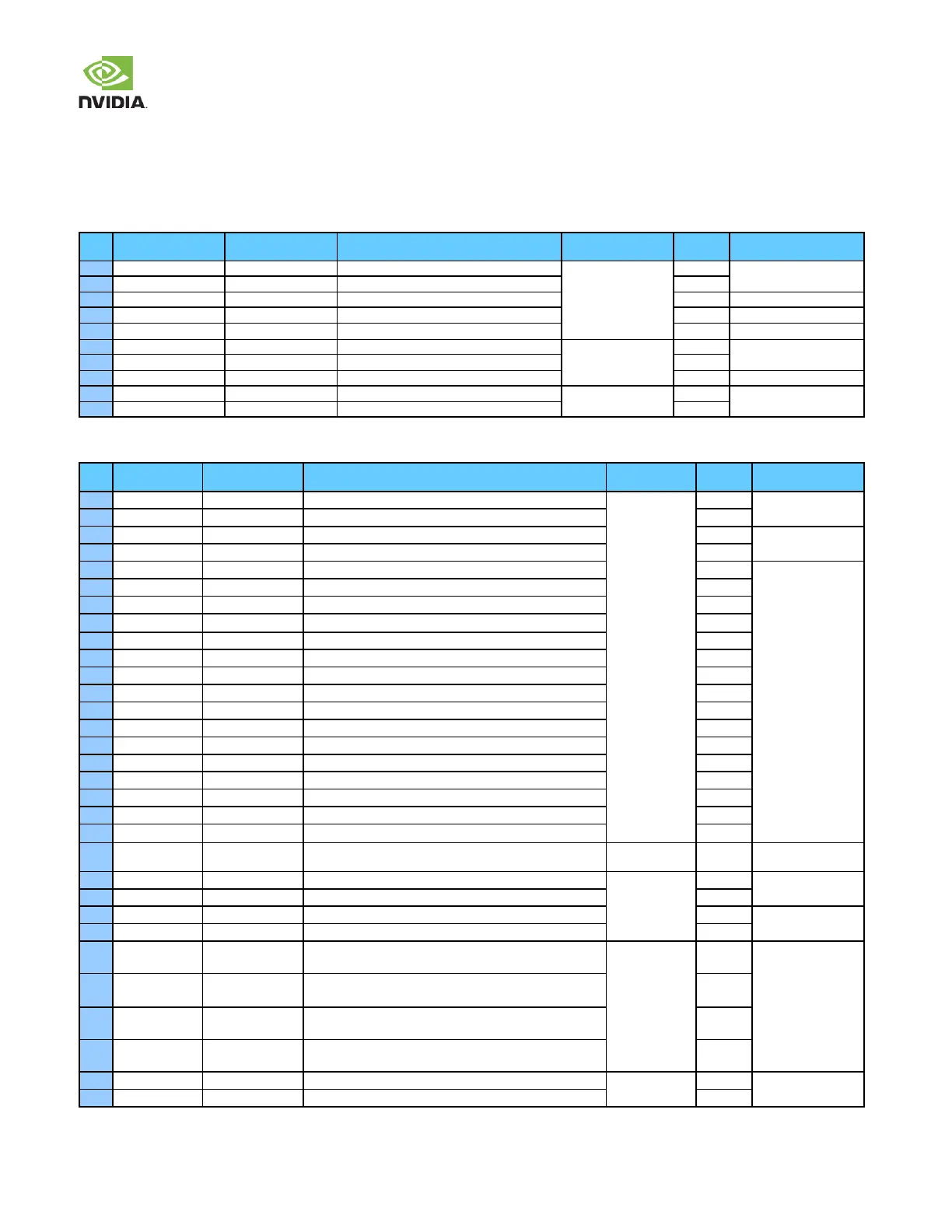

Table 14. USB 3.0, PCIe & SATA Pin Descriptions

Usage on the

Carrier Board

PCIe 0 Reference Clock+ (PCIe IF #0)

PCIe 0 Reference Clock (PCIe IF #0)

PCIe 0 Clock Request (PCIe IF #0)

Open Drain 3.3V, Pull-

up on the module

PCIe 0 Reset (PCIe IF #0)

PCIe 0 Lane 0 Receive+ (PCIe IF #0)

PCIe PHY, AC-Coupled

on carrier board

PCIe 0 Lane 0 Receive (PCIe IF #0)

PCIe 0 Lane 0 Transmit+ (PCIe IF #0)

PCIe 0 Lane 0 Transmit (PCIe IF #0)

USB SS 1 Receive+ (USB 3.0 Port #2 or PCIe IF #0 Lane 1)

USB SS 1 Receive (USB 3.0 Port #2 or PCIe #0 Lane 1)

USB SS 1 Transmit+ (USB 3.0 Port #2 or PCIe IF #0 Lane 1)

USB SS 1 Transmit (USB 3.0 Port #2 or PCIe #0 Lane 1)

PCIe 2 Receive+ (PCIe IF #0 Lane 2 or PCIe IF #1 Lane 0)

PCIe 2 Receive (PCIe IF #0 Lane 2 or PCIe IF #1 Lane 0)

PCIe 2 Transmit+ (PCIe IF #0 Lane 2 or PCIe IF #1 Lane 0)

PCIe 2 Transmit (PCIe IF #0 Lane 2 or PCIe IF #1 Lane 0)

PCIe RFU Receive+ (PCIe IF #0 Lane 3 or USB 3.0 Port #1)

PCIe RFU Receive (PCIe IF #0 Lane 3 or USB 3.0 Port #1)

PCIe RFU Transmit+ (PCIe IF #0 Lane 3 or USB 3.0 Port #1)

PCIe RFU Transmit (PCIe IF #0 Lane 3 or USB 3.0 Port #1)

Open Drain 3.3V, Pull-

up on the module

PCIe Reference Clock 1+ (PCIe IF #2)

PCIe Reference Clock 1 (PCIe IF #2)

PCIE 1 Clock Request (mux option - PCIe IF #2)

Open Drain 3.3V, Pull-

up on the module

PCIe 1 Reset (PCIe IF #2)

PCIe 1 Receive+ (PCIe #2 Lane 0 muxed w/USB 3.0 Port

#0)

USB 3.0 Type A

(Default) or M.2

Key E

PCIe PHY, AC-Coupled

on carrier board

PCIe 1 Receive (PCIe #2 Lane 0 muxed w/USB 3.0 Port

#0)

PCIe 1 Transmit+ (PCIe #2 Lane 0 muxed w/USB 3.0 Port

#0)

PCIe 1 Transmit (PCIe #2 Lane 0 muxed w/USB 3.0 Port

#0)

PCIe 2 Reference Clock+ (PCIe IF #1)

PCIe 2 Reference Clock (PCIe IF #1)

Loading...

Loading...