Manual for Advance 10B/Advance 10F

33

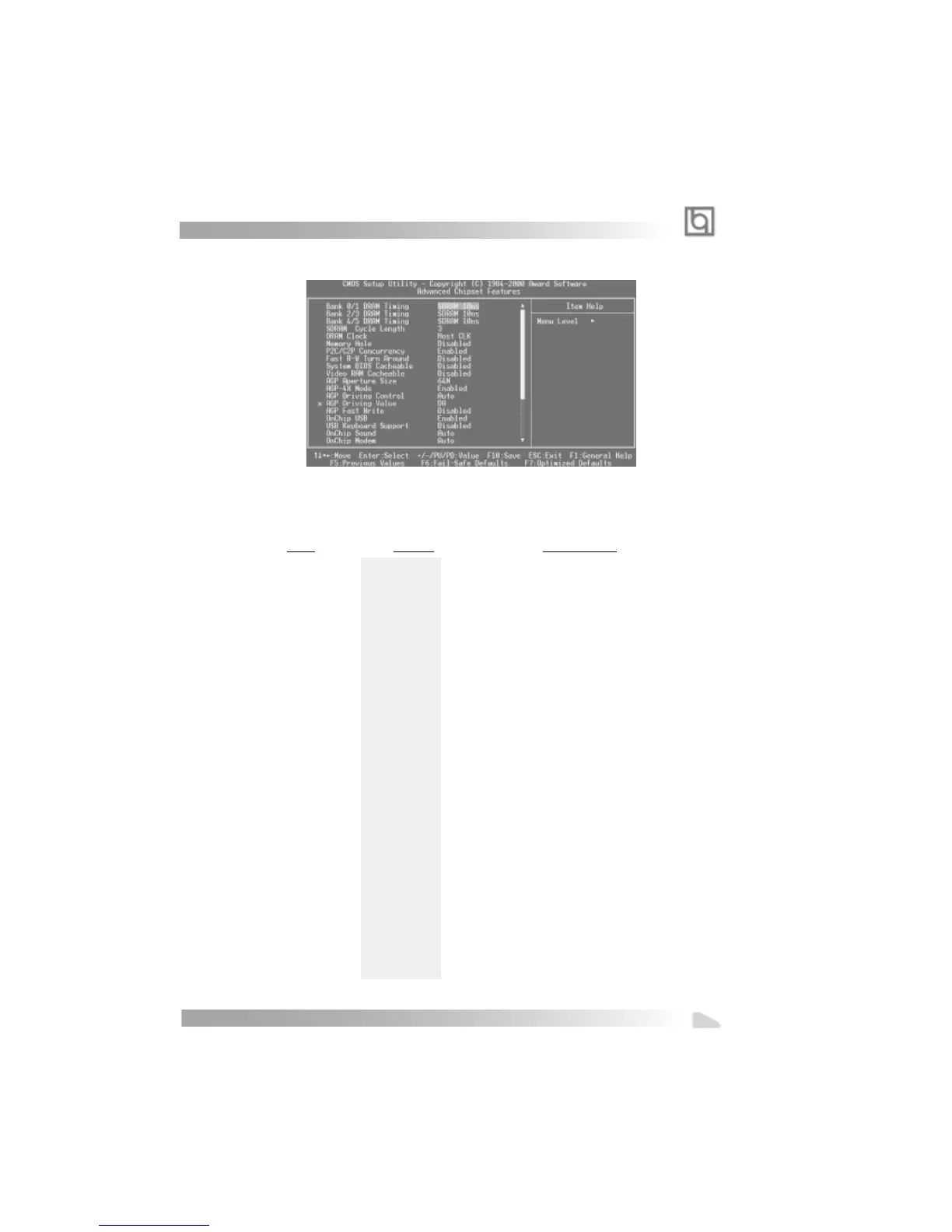

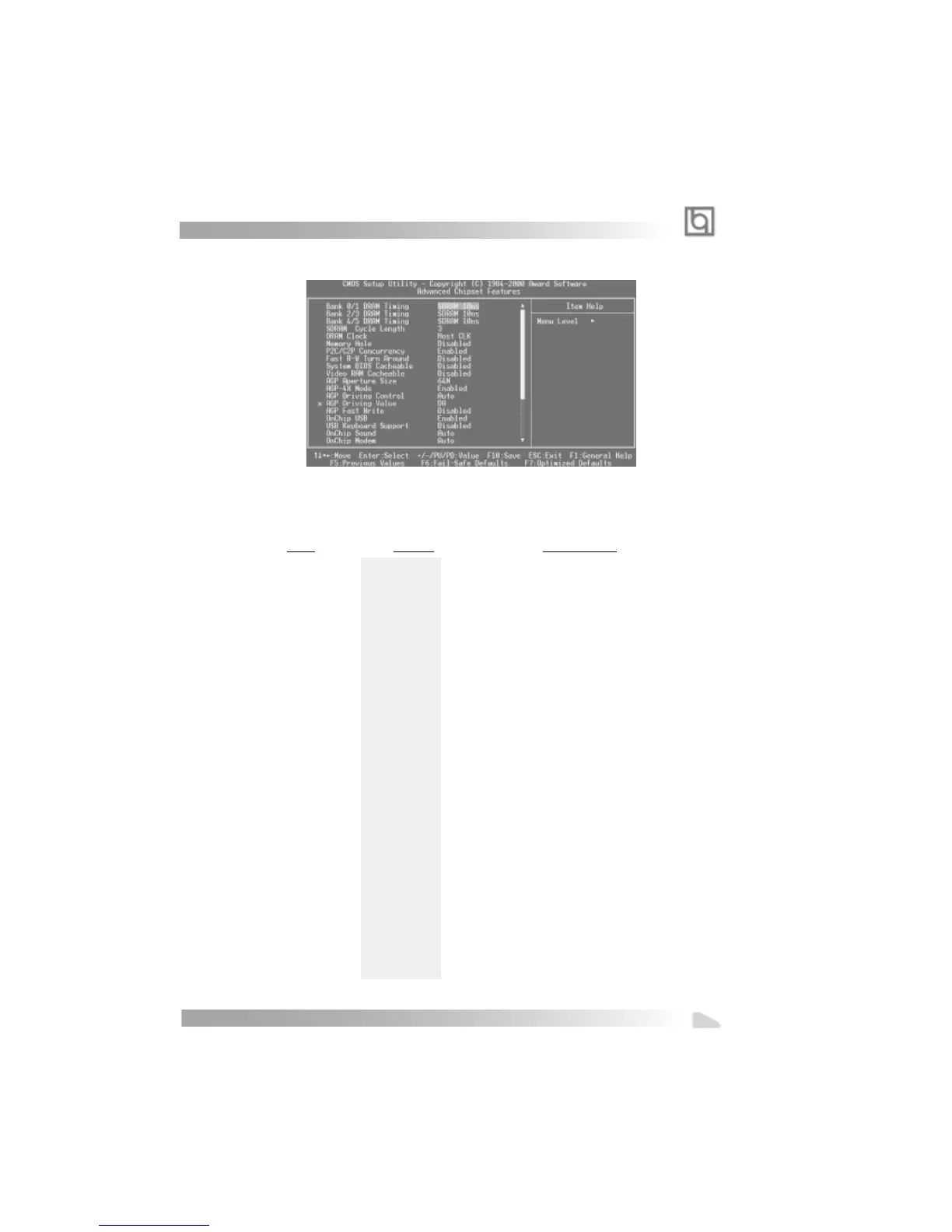

Advanced Chipset Features Setup

Figure-5 Advanced Chipset Features Setup Menu

The following indicates the options for each item and describes their meaning.

Item Option Description

l Bank 0/1, 2/3, 4/5 SDRAM 8/10ns These items are of selected DRAM read/write

DRAM Timing Normal timing. Default setting is recommended.

Medium

Fast

Turbo

l SDRAM Cycle 2/3 Define the CLT timing parameter of SDRAM

Length Auto expressed in 66MHz clocks.

Latency Time = 2 clocks

Latency Time = 3 clocks

l DRAM Clock Host Clk DRAM frequency same as CPU FSB

Hclk-33M DRAM frequency is faster than CPU FSB by 33MHz.

l Memory Hole Enabled Memory Hole at 15-16M is reserved for expanded

ISA card.

Disabled Do not set this memory hole.

l P2C/C2P Enabled Enabled P2C/C2P concurrency

Concurrency Disabled Disable P2C/C2P concurrency

l System BIOS Enabled Beside conventioal memory, system BIOS area is

Cacheable also cacheable.

Disabled System BIOS area is not cacheable.

l Video RAM Enabled Besides conventional memory, video RAM is also

Cacheable also cacheable.

Disabled Video RAM area is not cacheable.

Chapter 3

Loading...

Loading...